1/2017

Ускорение работы ЦАП на базе ШИМ

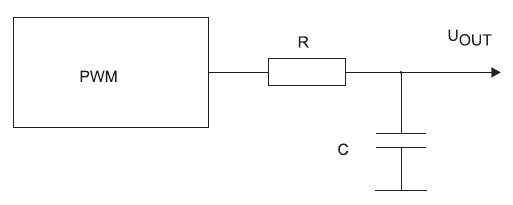

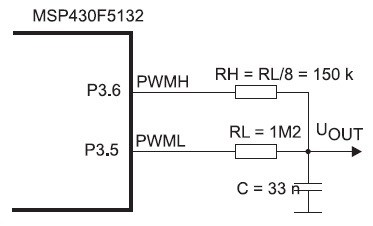

Рисунок 1. RC ФНЧ формирует среднее значение сигнала ШИМ

RC-фильтр удаляет переменные составляющие тока; то, что остаётся, является сигналом среднего значения UOUT. Если период T сигнала ШИМ равен 63 тактовым сигналам, то сигнал UOUT может иметь одно из 64 дискретных значений (от 0 до 63, 6-битовое разрешение).

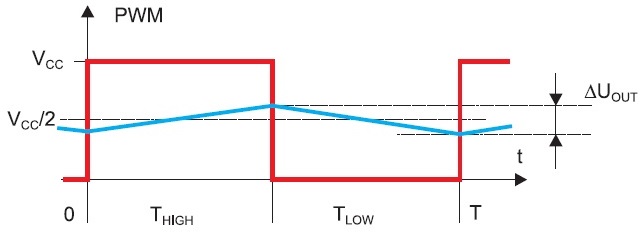

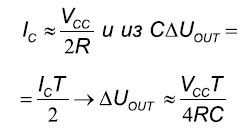

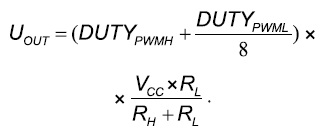

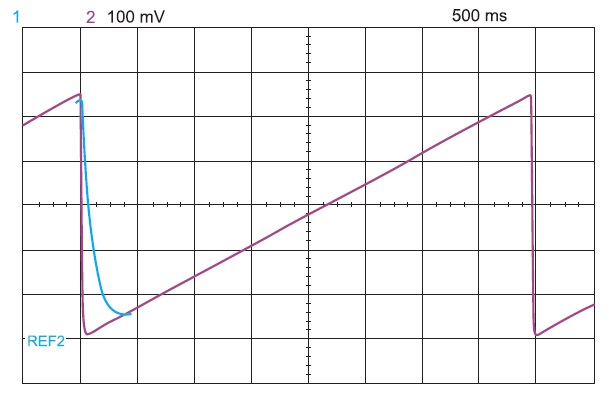

Рисунок 2. Выход фильтра (синий) должен иметь пульсации меньше одного LSb

Постоянная времени τ RC-фильтра нижних частот должна быть достаточно большой, чтобы сглаживать выходной сигнал UOUT. Пульсации ΔUOUT должны быть меньше одного младшего бита (LSb). Наихудший случай возникает при скважности, равной 50% (рисунок 2). Если τ значительно больше периода T, тогда заряжающий конденсатор ток IC и изменение ΔUOUT можно аппроксимировать следующим образом:

Для 6-битового ЦАП ΔUOUT должно быть меньше VCC/64, что требует от фильтра τ = RC ≥ 16 × T.

Некоторые полезные числа: в микропроцессорах низкой мощности часто используется кварцевый генератор частоты 32 768 Гц, и этот тактовый сигнал используется для блока ШИМ. При 6-битовой ШИМ период T составляет

Рисунок 3. Объединение двух выходов ЦАП на базе ШИМ

Блоки ШИМ в микроконтроллерах обычно могут генерировать более одного сигнала ШИМ. Рассмотрим суммирование выходов от двух 3-битовых ЦАП на базе ШИМ (ЦАПВ и ЦАПН), где выход ЦАПН сводится к одной восьмой амплитуды перед суммированием (рисунок 3). Результирующий сигнал действует как 6-битовый ЦАП, но с важным преимуществом перед простым вариантом: период T составляет только восемь периодов тактовых импульсов для такого же разрешения, а требуемая постоянная времени τ составляет 1/8 от предыдущей, ускоряя время успокоения в восемь раз. Такую схему легко реализовать с помощью резисторов в RC-фильтре для двух сигналов ШИМ (ШИМВ (PWMH), ШИМН (PWML)):

Выходной сигнал UOUT задаётся уравнением:

Так этот метод реализован в микроконтроллере TI MSP430F5132. Пример программы инициализации и записи в 6-битовый (3+3) ЦАП на базе ШИМ:

// configure PWM - 32 kHz / 8 = 4 kHz::

6 bit in two PWMs, done only once on power-up (конфигурировать ШИМ — 32 кГц / 8 = 4 кГц, 6 бит в двух ШИМ, выполняется один раз при включении питания)

TA0CCR0 = 7; // count up to 7 (including)

TA0CTL = TASSEL__ACLK | MC_1 | TACLR;

TA0CCR1 = 0; TA0CCTL1 = OUTMOD_6; // toggle/set

TA0CCR2 = 0; TA0CCTL2 = OUTMOD_6; // toggle/set

// use:: write to PWM block to achieve the desired DAC output (записать в блок ШИМ для получения нужного выхода ЦАП)

DAClevel++; // next DAC level, DAClevel is a char

TA0CCR1 = (DAClevel >> 3) & 7; // set PWMH: MSB 3 bits

TA0CCR2 = (DAClevel) & 7; // set PWML: LSB 3 bits

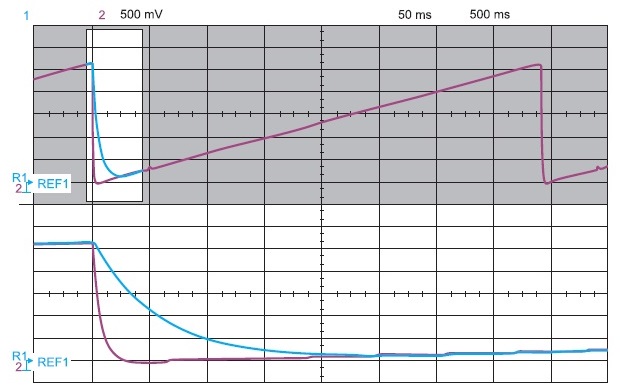

Рисунок 4. Выходные сигналы 6-битовых ЦАП на базе ШИМ. Синяя кривая — реализация, как на рисунке 1 (160 мс успокоения); фиолетовая кривая — реализация, как на рисунке 3 (20 мс успокоения)

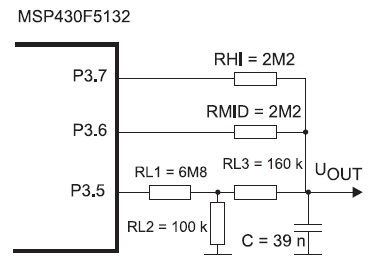

7-битовый ЦАП можно реализовать с использованием 1% резисторов (рисунок 5). На этот раз два сигнала ШИМ используются для создания двух трёхбитовых ЦАП, всего шесть битов, а старший бит (MSb) просто устанавливается в 0 или 1 на P3.7.

Рисунок 5. Реализация семибитового ЦАП на базе ШИМ

Программа инициализации и записи в 7-битовый (3+3+1) ЦАП на базе ШИМ:

// configure PWM — 32 kHz / 8 = 4 kHz::

7 bit in two PWMs and one digital pin, done only once on power-up

// is the same as given in configure section in figure 5

// use:: write to Timer comparators to achieve the desired DAC output

DAClevel++; // next DAC level, DAClevel is a char

TA0CCR1 = (DAClevel >> 3) & 7; // set PWMH, MSB, 3 bits

TA0CCR2 = (DAClevel) & 7; // set PWML, LSB, 3 bits

if (DAClevel & BIT6) P3OUT |= BIT7;

else P3OUT &= ~BIT7; // set MSB, no PWM

Здесь повышение скорости даже заметнее. Простой ЦАП на базе ШИМ должен будет иметь период, равный 128 периодам тактовой частоты (128/32768 s-1 = 3,9 мс), давая в результате τ, равное 32×Т = 125 мс и время успокоения, равное 5×125 мс = 625 мс. На рисунке 6 успокоение происходит за 40 мс — в 16 раз быстрее. ФНЧ более высокого порядка также помог бы сократить время успокоения.

Рисунок 6. Выходной сигнал схемы, показанной на рисунке 5; отметьте хорошую линейность