#### 8V19N880

RF Sampling Clock Generator and Jitter Attenuator

The 8V19N880 is a fully integrated FemtoClock<sup>®</sup> RF Sampling Clock Generator and Jitter Attenuator. The device is designed as a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards. The 8V19N880 is optimized to deliver excellent phase noise performance as required in 4G, 5G, and including mmWave radio implementations. The device supports JESD204B (subclass 0 and 1) and JESD204C.

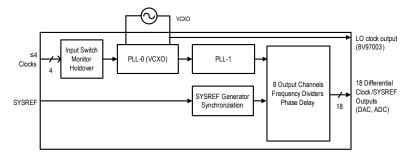

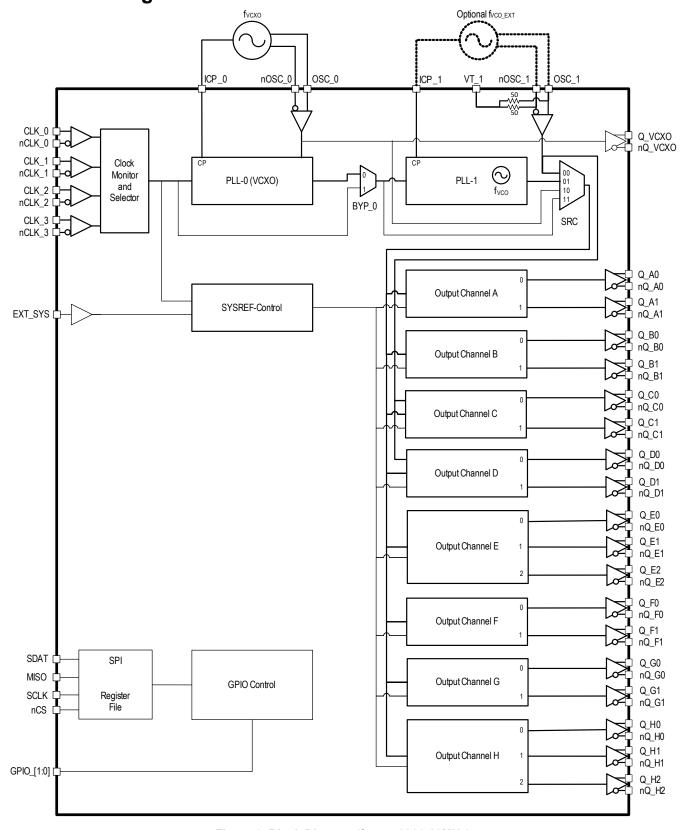

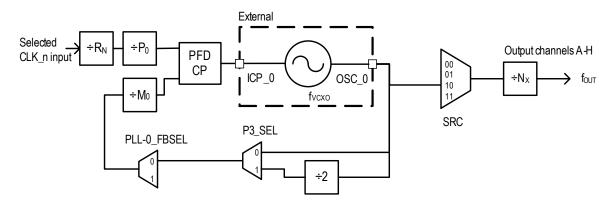

A two-stage PLL architecture supports both jitter attenuation and frequency multiplication. The first stage PLL is the jitter attenuator and uses an external VCXO for best possible phase noise characteristics. The second stage PLL locks on the first PLL output signal and synthesizes the target frequency. The second stage PLL can use the internal or an external high-frequency VCO.

The 8V19N880 generates the high-frequency clocks and the low-frequency synchronization signals (SYSREF) from the selected VCO. SYSREF signals are internally synchronized to the clock signals. The integrated signal delay blocks can be used to achieve phase alignment, controlled phase offsets between system reference and clock signals, and to align/delay individual output signals. The four redundant inputs are monitored for activity. Four selectable clock switching modes can handle clock input failure scenarios. Auto-lock, individually programmable output frequency dividers, and phase adjustment capabilities are added for flexibility.

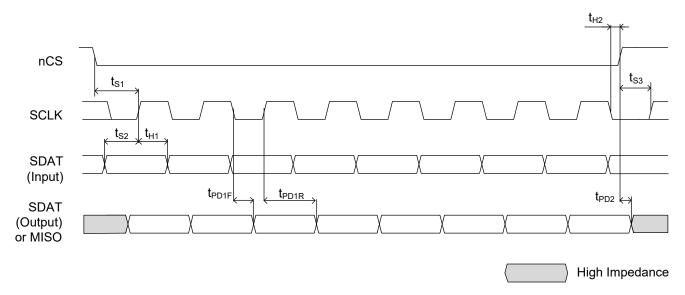

The 8V19N880 is configured through a 3/4-wire SPI interface and reports lock and signal loss status in internal registers and via the GPIO[1:0] outputs. Internal status bit changes can also be reported via a GPIO output.

#### **Features**

- High-performance clock RF sampling clock generator and clock jitter attenuator with support for JESD204B/C

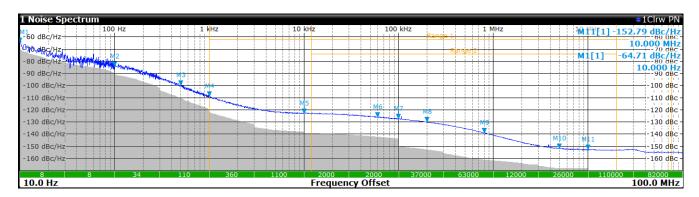

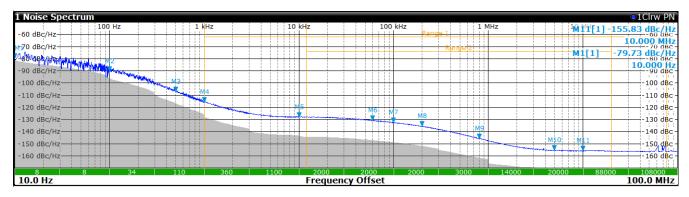

- Low phase noise: -144.7dBc/Hz (800kHz offset; 491.52MHz)

- Integrated phase noise of 74fs RMS (12k-20MHz, 491.52MHz)

- Dual-PLL architecture with internal and optional external VCO

- Eight output channels with a total of 18 outputs

- Configurable integer clock frequency dividers

- Clock output frequencies: up to 3932.16MHz (Internal VCO) and ≤ 6GHz (optional external VCO)

- Differential, low noise I/O

- Deterministic phase delay and integrated phase delay circuits

- Redundant input clock architecture with four inputs and monitors, holdover, and input switching

- SPI 3/4 wire configuration interface

- Supply voltage: 1.8V and 3.3V

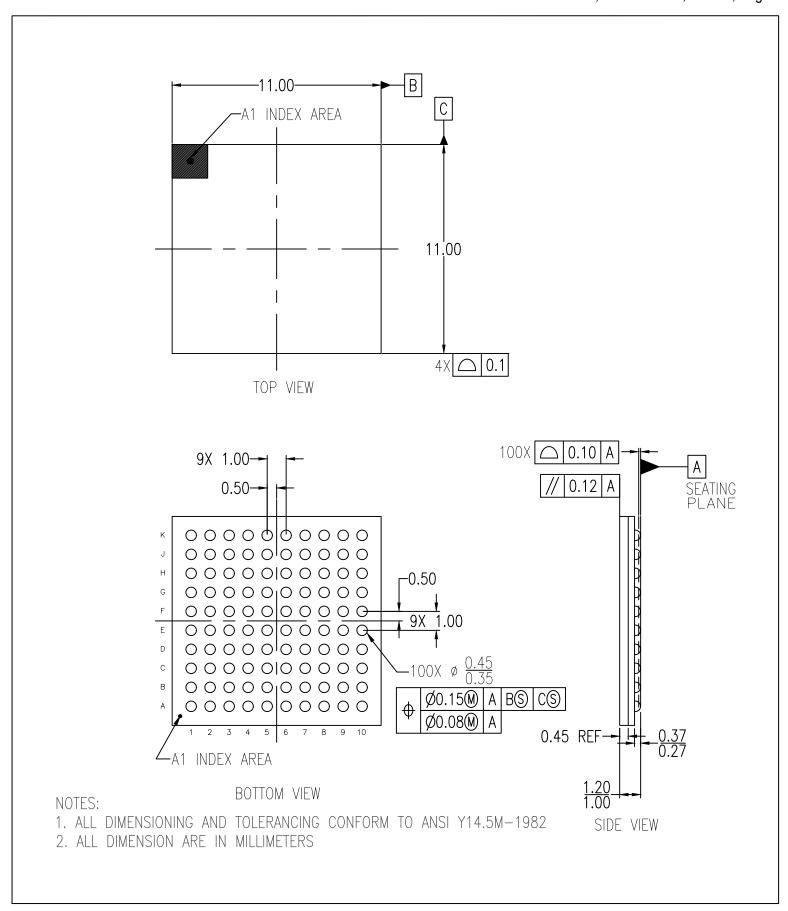

- Package: 100 CABGA (11 x 11 mm²)

- Temperature range: -40°C to +95°C (board)

## **Applicable Standards**

JESD204B and C

## **Applications**

- Wireless infrastructure applications: 4G, 5G, and mmWave

- Data acquisition: jitter-sensitive ADC and DAC circuits

- Radar, imaging, instrumentation, and medical

Figure 1. Simplified Block Diagram

# **Contents**

| 1. | Bloc       | Block Diagram     |                                              |    |  |  |

|----|------------|-------------------|----------------------------------------------|----|--|--|

| 2. | Featu      | res (Full List) . |                                              | 5  |  |  |

| 3. | Pin lı     | formation         |                                              | 6  |  |  |

|    | 3.1        | Pin Assignments   |                                              | 6  |  |  |

|    | 3.2        | Ū                 |                                              |    |  |  |

| 4. | Princ      | •                 | on                                           |    |  |  |

|    | 4.1        | •                 |                                              |    |  |  |

|    | 4.2        |                   | pop Operation                                |    |  |  |

|    |            |                   | ncy Generation                               |    |  |  |

|    |            | •                 | scription                                    |    |  |  |

|    |            |                   | ·<br>VCXO-PLL) Lock Detect                   |    |  |  |

|    |            |                   | ock Detect                                   |    |  |  |

|    | 4.3        |                   | and JESD204B/C Logic                         |    |  |  |

|    |            | •                 | l Description                                |    |  |  |

|    |            |                   | elay Circuits                                |    |  |  |

|    |            | 4.3.3 Differen    | tial Outputs                                 | 21 |  |  |

|    | 4.4        | Redundant Clock   | Inputs                                       | 23 |  |  |

|    |            | 4.4.1 Monitori    | ing and LOS of Input Signal                  | 23 |  |  |

|    |            | 4.4.2 Input Re    | e-Validation                                 | 23 |  |  |

|    |            | 4.4.3 Clock Se    | election                                     | 24 |  |  |

|    |            | 4.4.4 Holdove     | эг                                           | 24 |  |  |

|    |            | 4.4.5 Input Pr    | iorities                                     | 24 |  |  |

|    |            | 4.4.6 Hold-off    | Counter                                      | 24 |  |  |

|    | 4.5        | Revertive Switchi | ing                                          |    |  |  |

|    | 4.6        | Configuration for | JESD204B Operation                           | 25 |  |  |

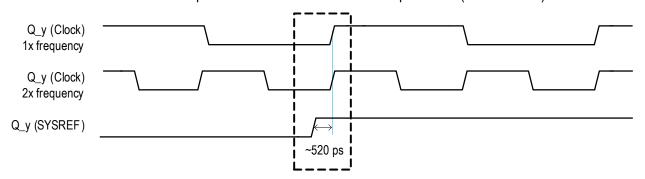

|    |            | 4.6.1 SYSREI      | F Generation                                 | 25 |  |  |

|    |            |                   | SYSREF Phase Alignment                       |    |  |  |

|    | 4.7        | ·                 | Input/Outputs (GPIO_[1:0])                   |    |  |  |

|    |            |                   | in Configuration                             |    |  |  |

|    |            |                   | in Configuration at Startup                  |    |  |  |

|    | 4.8        |                   | s and Interrupts                             |    |  |  |

|    | 4.9        |                   | atures                                       |    |  |  |

|    | 4.10       | •                 | Reset, and Synchronization                   |    |  |  |

|    |            |                   | mended Configuration Sequence (In Order)     |    |  |  |

|    | 4.11       | -                 | ng Frequency Dividers and Phase Delay Values |    |  |  |

| _  |            |                   |                                              |    |  |  |

| 5. | •          | •                 |                                              |    |  |  |

|    | 5.1<br>5.2 | •                 | tions                                        |    |  |  |

|    | 5.2        |                   | Configuration Registers                      |    |  |  |

|    |            |                   | LL-0 Frequency Divider and Control Registers |    |  |  |

|    |            | ' '               | Charge Pump Control Registers                |    |  |  |

|    |            |                   | nput and Bypass Control Registers            |    |  |  |

|    |            |                   | Charge Pump Control Registers                |    |  |  |

|    |            |                   | eedback Control Registers                    |    |  |  |

|    |            |                   | ice Switching Registers                      |    |  |  |

|    |            |                   |                                              |    |  |  |

### 8V19N880 Datasheet

|     |                    | 5.2.8      | SYSREF Control Registers                 | . 51 |  |  |

|-----|--------------------|------------|------------------------------------------|------|--|--|

|     |                    | 5.2.9      | Output Channel Registers                 | . 53 |  |  |

|     |                    | 5.2.10     | Output Registers                         | . 56 |  |  |

|     |                    | 5.2.11     | GPIO and Status Registers                |      |  |  |

|     |                    | 5.2.12     | Synchronization Control Registers        | 62   |  |  |

|     |                    | 5.2.13     | Output Enable Registers                  |      |  |  |

| 6.  | Elect              | rical Cha  | rracteristics                            | 64   |  |  |

|     | 6.1                | Absolute   | Maximum Ratings                          | . 64 |  |  |

|     | 6.2                | Recomn     | nended Operating Conditions              | . 64 |  |  |

|     | 6.3                | Pin Cha    | racteristics                             | 65   |  |  |

|     | 6.4                | DC Cha     | racteristics                             | 65   |  |  |

|     |                    | 6.4.1      | Supply Voltage and Power Consumption     | 65   |  |  |

|     |                    | 6.4.2      | LVCMOS I/O Characteristics               | 67   |  |  |

|     | 6.5                | Different  | ial I/O Characteristics                  | . 68 |  |  |

|     | 6.6                | AC Chai    | racteristics                             | . 69 |  |  |

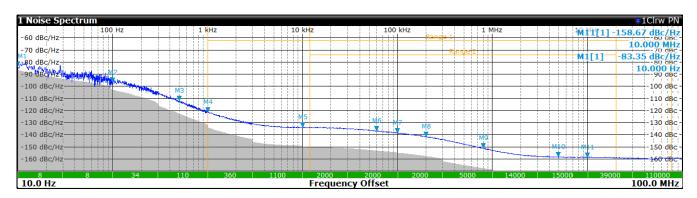

| 7.  | Cloc               | k Phase I  | Noise Characteristics                    | . 78 |  |  |

| 8.  | Appli              | ication In | formation                                | . 79 |  |  |

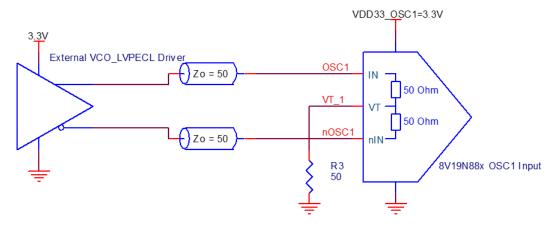

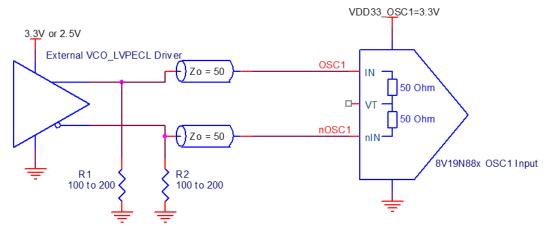

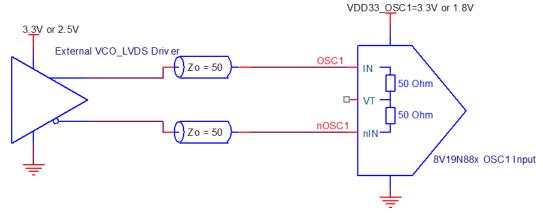

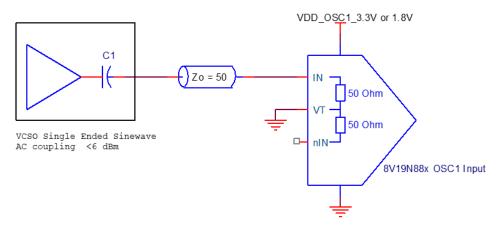

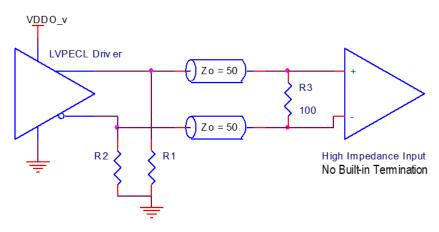

|     | 8.1                | OSC 1      | Input Termination (External VCO)         | . 79 |  |  |

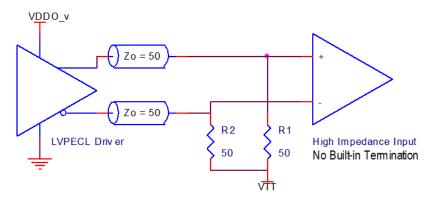

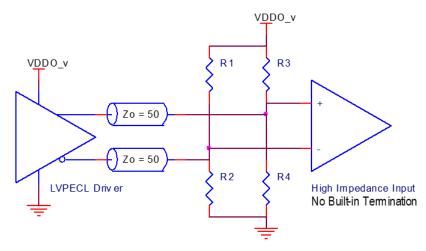

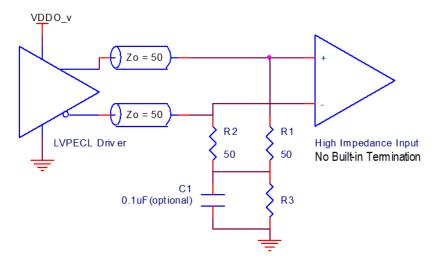

|     | 8.2                | _          | tion for Differential Q y LVPECL Outputs |      |  |  |

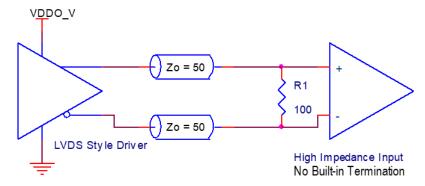

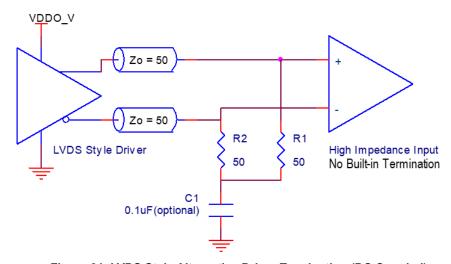

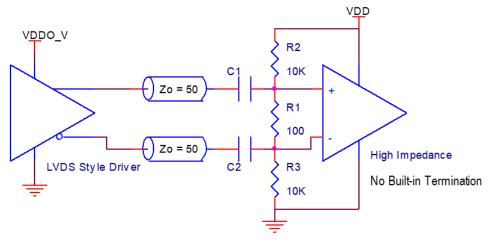

|     | 8.3                | Termina    | tion for Differential Q_y LVDS Outputs   | . 82 |  |  |

| 9.  | Ther               | mal Char   | acteristics                              | 84   |  |  |

|     | 9.1                | Tempera    | ature Considerations                     | . 84 |  |  |

| 10. | Pack               | age Outli  | ine Drawings                             | . 85 |  |  |

| 11. | Orde               | ring Info  | rmation                                  | . 85 |  |  |

| 12. | -                  |            |                                          |      |  |  |

| 13. | Glossary           |            |                                          |      |  |  |

|     | Revision History 8 |            |                                          |      |  |  |

|     |                    |            |                                          |      |  |  |

# 1. Block Diagram

Figure 2. Block Diagram (f<sub>VCO</sub> = 3932.16MHz)

## 2. Features (Full List)

- High-performance clock RF-PLL with support for JESD204B/C

- Low phase noise: -144.7dBc/Hz (800kHz offset; 491.52MHz)

- Integrated phase noise of 74fs RMS (12k-20MHz, 491.52MHz)

- Dual-PLL architecture with optional external VCO

- 1st-PLL stage with external VCXO for clock jitter attenuation

- 2nd-PLL with internal FemtoClockNG PLL: 3932.16MHz

- · Optional external VCO frequency range: 700MHz to 6GHz

- Eight output channels with a total of 18 outputs, organized in:

- Two RF clock channels each consisting of two device clocks (≤ 4GHz)/SYSREF outputs; each output can buffer external VCO clocks up to 6GHz

- Six device clock/SYSREF channels (2 or 3 outputs, ≤ 4GHz)

- · One VCXO-PLL (PLL-0) output

- Configurable integer clock frequency dividers

- Supported clock output frequencies include:

- From internal VCO: 3932.16, 1966.08, 983.04, 491.52 and 245.76MHz

- From external VCO: ≤ 6GHz

- Low-power LVPECL/LVDS outputs support configurable signal amplitude, DC and AC coupling and LVPECL,

LVDS line terminations techniques

- Phase delay circuits

- · PLL feedback phase delay for output-to-input alignment

- · Channel phase delay with 512 steps of 127ps

- Individual SYSREF output phase delay with steps of 254ps and 30ps analog delay for output alignment

- Redundant input clock architecture with four inputs and the following:

- · Input activity monitoring

- · Manual and automatic, fault-triggered clock selection modes

- · Priority controlled clock selection

- · Digital holdover and smooth input clock switching

- Differential inputs accept LVDS and LVPECL signals

- SYSREF generation modes include internal and external trigger mode for JESD204B/C

- SPI 3/4 wire configuration interface

- Supply voltage: 1.8V (core, outputs) and 3.3V (oscillator interfaces, 6GHz output supply)

- Supply voltage: 1.8V (core), 3.3V (oscillator interfaces, 6GHz output supply), 1.8V and 3.3V (channel C, D output supplies)

- SPI and control I/O voltage: 1.8V

- Package: 100 CABGA (11 x 11 mm²)

- Temperature range: -40°C to +95°C (board)

# 3. Pin Information

# 3.1 Pin Assignments

| Α | Q_A1          | Q_A0        | GND        | (ICP_0)       | OSC_0          | Q_VC<br>XO     | GND           | Q_H2  | Q_H1    | Q_H0        |

|---|---------------|-------------|------------|---------------|----------------|----------------|---------------|-------|---------|-------------|

| В | (nQ_A1)       | nQ_A0       | GND        | VDD33<br>_CP0 | nOSC_0         | nQ_VC<br>XO    | GND           | nQ_H2 | nQ_H1   | nQ_H0       |

| С | VDDO_<br>QA   | VDDO_<br>QB | GND        | GND           | GND            | (VDD_<br>OSCO) | GND           | GND   | VDDO_QG | VDDO_<br>QH |

| D | nQ_B1         | Q_B1        | nQ_B0      | Q_B0          | (VDD<br>_SPI   | EXT_<br>SYS    | nQ_G1         | Q_G1  | nQ_G0   | Q_G0        |

| Ε | VDDO3<br>3_QC | GND         | MISO       | SCLK          | SDAT           | nCS            | VDD_I<br>NPUT | GND   | GND     | VDDO_<br>QF |

| F | Q_C1          | Q_C0        | GPIO_      | CLK3          | CLK2           | (CLK1)         | CLKO          | GND   | Q_F0    | Q_F1        |

| G | nQ_C1         | nQ_C0       | GPIO_<br>1 | nCLK3         | nCLK2          | nCLK1          | nCLK0         | GND   | nQ_F0   | nQ_F1       |

| Н | VDDO3<br>3_QD | GND         | GND        | GND           | GND            | GND            | GND           | GND   | GND     | VDDO<br>_QE |

| J | Q_D0          | Q_D1        | nOSC_1     | VT_1          | VCO_<br>CAP    | ICP_1          | GND           | Q_E2  | Q_E1    | Q_E0        |

| K | nQ_D0         | nQ_D1       | OSC_1      | VDD33<br>OSC1 | VDD 33<br>_VCO | VDD 33<br>_CP1 | VDD_<br>PLL1  | nQ_E2 | nQ_E1   | nQ_E0       |

| l | 10            | 9           | 8          | 7             | 6              | 5              | 4             | 3     | 2       | 1           |

Figure 3. Pin Assignments for 11 x 11 mm² 100 CABGA Package (Bottom View)

# 3.2 Pin Descriptions

**Table 1. Pin Descriptions**

| Pin         | Name                           | Type <sup>[1]</sup>              |         | Description                                                                                                                                                                          |  |  |  |

|-------------|--------------------------------|----------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             | Clock and SYSREF Signal Inputs |                                  |         |                                                                                                                                                                                      |  |  |  |

| F4          | CLK_0                          | Input                            | PD      | Device clock 0 non-inverting and inverting differential clock input. Inverting                                                                                                       |  |  |  |

| G4          | nCLK_0                         |                                  | PD/PU   | input is biased to ~1.05V by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                           |  |  |  |

| F5          | CLK_1                          | Input                            | PD      | Device clock 1 non-inverting and inverting differential clock input. Inverting input is biased to ~1.05V by default when left floating. Compatible with                              |  |  |  |

| G5          | nCLK_1                         |                                  | PD/PU   | LVPECL, LVDS and LVCMOS signals.                                                                                                                                                     |  |  |  |

| F6          | CLK_2                          | Input                            | PD      | Device clock 2 non-inverting and inverting differential clock input. Inverting                                                                                                       |  |  |  |

| G6          | nCLK_2                         |                                  | PD/PU   | input is biased to ~1.05V by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                           |  |  |  |

| F7          | CLK_3                          | Input                            | PD      | Device clock 3 non-inverting and inverting differential clock input. Inverting                                                                                                       |  |  |  |

| G7          | nCLK_3                         |                                  | PD/PU   | input is biased to ~1.05V by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                           |  |  |  |

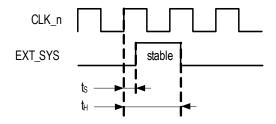

| D5          | EXT_SYS                        | Input                            | PD      | External SYSREF pulse trigger input. 1.8V LVCMOS interface levels.                                                                                                                   |  |  |  |

|             |                                |                                  | Externa | al Oscillator Interface Pins                                                                                                                                                         |  |  |  |

| A7          | ICP_0                          | Output                           |         | PLL-0 (VCXO-PLL) charge pump output. Connect to the frequency control input of the external VCXO and to the loop filter.                                                             |  |  |  |

| A6          | OSC_0                          | Input                            | PD      | VCXO non-inverting and inverting differential clock input. Inverting input is                                                                                                        |  |  |  |

| В6          | nOSC_0                         |                                  | PD/PU   | biased to ~1.05V by default when left floating. Compatible with LVPECL, LVDS, and LVCMOS signals.                                                                                    |  |  |  |

| J5          | ICP_1                          | Output                           |         | PLL-1 charge pump output. Connect to the frequency control input of the external VCO and the loop filter. Leave open if PLL-1 is not used (bypassed).                                |  |  |  |

| K8          | OSC_1                          | Input                            | 50Ω     | External VCO non-inverting and inverting differential clock input.                                                                                                                   |  |  |  |

| J8          | nOSC_1                         |                                  | 50Ω     | Compatible with LVPECL and LVDS signals, also accepts single-ended sinusoidal signals on the OSC_1 pin.                                                                              |  |  |  |

| J7          | VT_1                           | Termination 50Ω to OSC_1, nOSC_1 |         | Input for termination. Both OSC_1 and nOSC_1 inputs are internally terminated $50\Omega$ to this pin. For input termination information, see OSC_1 Input Termination (External VCO). |  |  |  |

|             |                                | •                                | Cloc    | k and SYSREF Outputs                                                                                                                                                                 |  |  |  |

| A9,<br>B9   | Q_A0,<br>nQ_A0                 | Output                           |         | Differential clock/SYSREF output A0 (Channel A). Configurable LVPECL/LVDS style and amplitude.                                                                                       |  |  |  |

| A10,<br>B10 | Q_A1,<br>nQ_A1                 | Output                           |         | Differential clock/SYSREF output A1 (Channel A). Configurable LVPECL/LVDS style and amplitude.                                                                                       |  |  |  |

| D7,<br>D8   | Q_B0,<br>nQ_B0                 | Output                           |         | Differential clock/SYSREF output B0 (Channel B). Configurable LVPECL/LVDS style and amplitude.                                                                                       |  |  |  |

| D9,<br>D10  | Q_B1,<br>nQ_B1                 | Output                           |         | Differential clock/SYSREF output B1 (Channel B). Configurable LVPECL/LVDS style and amplitude.                                                                                       |  |  |  |

| F9,<br>G9   | Q_C0,<br>nQ_C0                 | Output                           |         | Differential clock/SYSREF output C0 (Channel C). LVPECL style and configurable amplitude.                                                                                            |  |  |  |

| F10,<br>G10 | Q_C1,<br>nQ_C1                 | Output                           |         | Differential clock/SYSREF output C1 (Channel C). LVPECL style and configurable amplitude.                                                                                            |  |  |  |

| J10,<br>K10 | Q_D0,<br>nQ_D0                 | Output                           |         | Differential clock/SYSREF output D0 (Channel D). LVPECL style and configurable amplitude.                                                                                            |  |  |  |

Table 1. Pin Descriptions (Cont.)

| Pin Name Type <sup>[1]</sup> |                    |                  | e <sup>[1]</sup> | Description                                                                                                                    |

|------------------------------|--------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| J9,<br>K9                    | Q_D1,<br>nQ_D1     | Output           |                  | Differential clock/SYSREF output D1 (Channel D). LVPECL style and configurable amplitude.                                      |

| J1,<br>K1                    | Q_E0,<br>nQ_E0     | Output           |                  | Differential clock/SYSREF output E0 (Channel E). Configurable LVPECL/LVDS style and amplitude.                                 |

| J2,<br>K2                    | Q_E1,<br>nQ_E1     | Output           |                  | Differential clock/SYSREF output E1 (Channel E). Configurable LVPECL/LVDS style and amplitude.                                 |

| J3,<br>K3                    | Q_E2,<br>nQ_E2     | Output           |                  | Differential clock/SYSREF output E2 (Channel E). Configurable LVPECL/LVDS style and amplitude.                                 |

| F2,<br>G2                    | Q_F0,<br>nQ_F0     | Output           |                  | Differential clock/SYSREF output F0 (Channel F). Configurable LVPECL/LVDS style and amplitude.                                 |

| F1,<br>G1                    | Q_F1,<br>nQ_F1     | Output           |                  | Differential clock/SYSREF output F1 (Channel F). Configurable LVPECL/LVDS style and amplitude.                                 |

| D1,<br>D2                    | Q_G0,<br>nQ_G0     | Output           |                  | Differential clock/SYSREF output G0 (Channel G). Configurable LVPECL/LVDS style and amplitude.                                 |

| D3,<br>D4                    | Q_G1,<br>nQ_G1     | Output           |                  | Differential clock/SYSREF output G1 (Channel G). Configurable LVPECL/LVDS style and amplitude.                                 |

| A1,<br>B1                    | Q_H0,<br>nQ_H0     | Output           |                  | Differential clock/SYSREF output H0 (Channel H). Configurable LVPECL/LVDS style and amplitude.                                 |

| A2,<br>B2                    | Q_H1,<br>nQ_H1     | Output           |                  | Differential clock/SYSREF output H1 (Channel H). Configurable LVPECL/LVDS style and amplitude.                                 |

| A3,<br>B3                    | Q_H2,<br>nQ_H2     | Output           |                  | Differential clock/SYSREF output H2 (Channel H). Configurable LVPECL/LVDS style and amplitude.                                 |

| A5,<br>B5                    | Q_VCXO,<br>nQ_VCXO | Output           |                  | Differential PLL-0 (VCXO-PLL) clock outputs. Configurable LVPECL/LVDS style.                                                   |

|                              |                    |                  |                  | Control I/O                                                                                                                    |

| F8                           | GPIO_0             | Input/<br>Output | PD               | Configurable control input/status output pin 0. 1.8V LVCMOS interface levels.                                                  |

| G8                           | GPIO_1             | Input/<br>Output | PD               | Configurable control input/status output pin 1. 1.8V LVCMOS interface levels.                                                  |

| E6                           | SDAT               | Input/<br>Output | PU               | SPI serial configuration interface data pin. Input/Output in SPI 3-wire mode. Input in 4-wire SPI mode. 1.8V interface levels. |

| E7                           | SCLK               | Input            | PD               | SPI serial configuration interface clock pin. 1.8V interface levels.                                                           |

| E5                           | nCS                | Input            | PU               | SPI serial configuration interface chip-select pin. 1.8V interface levels.                                                     |

| E8                           | MISO               | Output           |                  | SPI serial configuration interface data output (in SPI 4-wire mode). Not used in SPI 3-wire mode. 1.8V interface levels.       |

|                              |                    | F                | ower Sup         | ply, Ground (GND), and Bypass                                                                                                  |

| C10                          | VDDO_QA            | Power            |                  | Positive supply voltage (1.8V) for the Q_A[1:0] outputs.                                                                       |

| C9                           | VDDO_QB            | Power            |                  | Positive supply voltage (1.8V) for the Q_B[1:0] outputs.                                                                       |

| E10                          | VDDO33_QC          | Power            |                  | Positive supply voltage (3.3V) for the Q_C[1:0] outputs.                                                                       |

| H10                          | VDDO33_QD          | Power            |                  | Positive supply voltage (3.3V) for the Q_D[1:0] outputs.                                                                       |

| H1                           | VDDO_QE            | Power            |                  | Positive supply voltage (1.8V) for the Q_E[2:0] outputs.                                                                       |

| E1                           | VDDO_QF            | Power            |                  | Positive supply voltage (1.8V) for the Q_F[1:0] outputs.                                                                       |

| C2                           | VDDO_QG            | Power            |                  | Positive supply voltage (1.8V) for the Q_G[1:0] outputs.                                                                       |

| 02                           | ADDO_66            | rowei            |                  | r ositive supply voltage (1.0v) for the Q_G[1.0] outputs.                                                                      |

Table 1. Pin Descriptions (Cont.)

| Pin                                                                                                        | Name       | Type <sup>[1]</sup> | Description                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------|------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| C1                                                                                                         | VDDO_QH    | Power               | Positive supply voltage (1.8V) for the Q_H[2:0] outputs.                                                                                         |

| В7                                                                                                         | VDD33_CP0  | Power               | Positive supply voltage (3.3V) for the charge pump output of PLL-0.                                                                              |

| K5                                                                                                         | VDD33_CP1  | Power               | Positive supply voltage (3.3V) for the charge pump output of PLL-1.                                                                              |

| C5                                                                                                         | VDD_OSC0   | Power               | Positive supply voltage (1.8V) for the OSC_0 input and Q_VCXO outputs.                                                                           |

| K7                                                                                                         | VDD33_OSC1 | Power               | Positive supply voltage (3.3V, 1.8V) for the OSC_1 input. This pin can also be supplied by 1.8V for setting the OSC_1 interface voltage to 1.8V. |

| K6                                                                                                         | VDD33_VCO  | Power               | Positive supply voltage (3.3V) for the internal VCO of PLL-1.                                                                                    |

| D6                                                                                                         | VDD_SPI    | Power               | Positive supply voltage (1.8V) for the SPI interface.                                                                                            |

| E4                                                                                                         | VDD_INPUT  | Power               | Positive supply voltage (1.8V) for the differential clock inputs CLK0-3.                                                                         |

| K4                                                                                                         | VDD_PLL1   | Power               | Positive supply voltage (1.8V) for PLL-1.                                                                                                        |

| J6                                                                                                         | VCO_CAP    | Analog              | Internal VCO regulator bypass capacitor. Use a 1.0 µF capacitor from this pin to GND.                                                            |

| A4, A8,<br>B4, B8,<br>C3, C4,<br>C6, C7,<br>C8, E2,<br>E3, E9,<br>F3, G3,<br>H2, H3,<br>H4, H5,<br>H6, H7, | GND        | Power               | Ground supply voltage (GND) and ground return path. Connect to board GND (0V).                                                                   |

PU (pull-up) and PD (pull-down) indicate internal input resistors (for values, see Table 57).

## 4. Principles Of Operation

#### 4.1 Overview

The 8V19N880 generates low-phase noise, synchronized clock and SYSREF output signals locked to an input reference frequency. The device contains two PLLs with configurable frequency dividers. The first PLL (VCXO-PLL or PLL-0) uses an external VCXO (f<sub>VCXO</sub>) as the oscillator and provides jitter attenuation to the input signal. The external loop filter is used to set the VCXO-PLL bandwidth frequency in conjunction with internal parameters. A VCXO buffer output is available for cascading multiple devices or to drive other clock devices at the VCXO frequency.

The second, low-phase noise PLL (PLL-1) multiplies the PLL-0 frequency to a high frequency from which all output signals are generated. PLL-1 can use an external oscillator (VCO, f<sub>VCO</sub>) in the range of 700MHz to 6GHz, or use the internal oscillator of 3932.16MHz. The use of the internal oscillator is sufficient for most applications; only applications requiring extraordinary low phase noise or frequency plans can use an external oscillator for PLL-1. Each PLL can be bypassed. PLL-0 bypass is recommended for applications with clean input clock signals: PLL-1 will synthesize the output clock signals directly from the selected input. The PLL-0-bypass mode does not require an external VCXO component.

If the VCXO frequency is suitable as the highest application frequency, PLL-1 can be bypassed.

The output of PLL-1 (output of PLL-0 if PLL-1 is bypassed) provides a central timing reference point for all output signals. From this point, fully synchronous dividers generate the output frequencies and the internal timing references for JESD204B/C support.

The device supports the generation of SYSREF pulses synchronous to the clock signals. There are eight output channels, each can be configured as a clock or SYSREF channel. The clock outputs are configurable with support for LVPECL or LVDS formats and a variable output amplitude. Each channel and each output offer adjustable phase delay functionality. Individual outputs and channels and unused circuit blocks support powered-down states for operating at lower power consumption.

The synchronous design allows an operation mode with deterministic phase delay between the active input and any clock and SYSREF output and also allows zero-delay configurations. Desired input-to-output and output-to-output phase relations can be configured by the programmable phase delay circuits. The deterministic delay capabilities support cascading multiple devices.

For redundancy purpose, there are four selectable reference frequency inputs and a configurable switch logic with priority-controlled auto-selection and holdover support.

The register map, which is accessible through the SPI interface with read-back capability, controls the main device settings and delivers device status information. Two configurable I/O pins can be used for general-purpose I/O, control, or status signaling functions.

## 4.2 Phase-Locked Loop Operation

#### 4.2.1 Frequency Generation

The 8V19N880 generates output frequencies in one of three modes: dual PLL mode, frequency synthesizer mode, and PLL-0 mode. Frequency dividers must be set by the user to match input and oscillator frequencies to achieve frequency and phase lock on the used PLLs. The frequency of the external VCXO and external VCO (if used) is selected by the user; the internal VCO frequency of PLL-1 is set to 3932.16MHz.

Table 2. PLL Modes

| Mode                  | Description                                                    | Configuration             |

|-----------------------|----------------------------------------------------------------|---------------------------|

| Dual PLL              | Input jitter attenuation                                       | BYP_0 = 0, SRC = 00 or 01 |

| Frequency Synthesizer | Frequency generation without jitter attenuation                | BYP_0 = 1, SRC = 00 or 01 |

| VCXO-PLL              | Input jitter attenuation, output frequency ≤ f <sub>VCXO</sub> | SRC = 10                  |

| PLL Bypass            | Fanout buffer/frequency divider                                | SRC = 11, BYP_0 = 1       |

#### 4.2.1.1 Dual PLL Mode

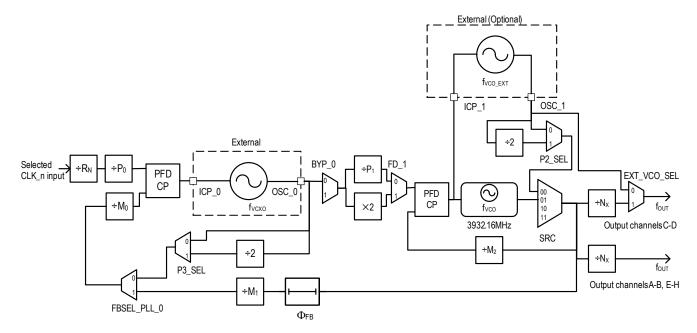

Application for the dual PLL mode is input clock jitter attenuation and frequency generation. PLL-0 must use an external VCXO and PLL-1 uses the internal VCO or an external VCO for frequency generation. Set BYP\_0 = 0. The dividers for both PLLs must be configured to achieve frequency lock. Figure 4 displays a detailed circuit and Table 3 shows the available frequency dividers for this mode. For information on selecting the feedback path for this mode, see PLL Feedback Path. Input to output delay is deterministic when the device is configured in dual PLL mode and the PLL feedback path is set through both  $M_0$  and  $M_1$  feedback divider (FBSEL\_PLL\_0 = 1).

Figure 4. Dual PLL Mode

Table 3. Dual PLL Mode Settings and Divider Values

| Divider                                                | Range               | Operation for f <sub>VCO</sub> = 3932.16MHz <sup>[1]</sup>                                                            |

|--------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|

| Input Divider R <sub>N</sub> <sup>[2]</sup>            | ÷1, ÷2, ÷4, ÷8      | Input clock frequency (FBSEL_PLL_0 = 1):                                                                              |

| PLL-0 Pre-Divider P <sub>0</sub>                       | ÷1÷32,767: (15 bit) | $f_{CLK} = R_N \times P_0 \times \frac{f_{VCXO}}{P_1} \times \frac{M_2}{M_0 \times M_1}$                              |

| PLL-0 Feedback Divider M <sub>0</sub>                  | ÷1÷32,767: (15 bit) | 0 P1 M0×M1                                                                                                            |

| PLL-0/1 Feedback Divider M <sub>1</sub> <sup>[3]</sup> | ÷1÷16,383: (14 bit) |                                                                                                                       |

| PLL-1 Pre-Divider P <sub>1</sub>                       | ÷1÷127: (7 bit)     | VCXO frequency:                                                                                                       |

| Frequency Doubler                                      | FD_1 = ×1 or ×2     | $f_{VCXO} = f_{VCO} \times \frac{P_1}{M_2}$                                                                           |

| PLL-1 Feedback Divider M <sub>2</sub> <sup>[4]</sup>   | ÷1÷1,023: (10 bit)  | P <sub>1</sub> : Set P <sub>1</sub> to 0.5 in above equation if the frequency doubler is engaged by setting FD_1 = 1. |

| Divider                              | Range                                                                            | Operation for f <sub>VCO</sub> = 3932.16MHz <sup>[1]</sup> |

|--------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------|

| Clock Output Divider N <sub>x</sub>  | ÷1÷20,480                                                                        | Output clock frequency:                                    |

| (x = A, B, C, D, E, F, G, H)         | N = $\{1,2,3,4,5\} \times 2^{m}$ with m = 0 to 12                                | $f_{OUT} = \frac{f_{VCO}}{N_X}$                            |

| SYSREF Output Divider N <sub>x</sub> | ÷1÷83,886,080                                                                    | Output SYSREF frequency:                                   |

| (x = A, B, C, D, E, F, G, H)         | N = $\{1,2,3,4,5\} \times 2^m \times 2^p$ with m<br>= 0 to 12 and<br>p = 1 to 12 | $f_{OUT} = \frac{f_{VCO}}{N_X}$                            |

Table 3. Dual PLL Mode Settings and Divider Values (Cont.)

- 1. External VCO operation: use the frequency of the external VCO for f<sub>VCO</sub> in above equations. For external VCO frequencies greater than 4GHz, set P2\_SEL to select the ÷2 path to reduce the external VCO frequency and enter f<sub>VCO</sub>÷2 as VCO frequency in above equations.

- 2. Input divider  $R_N$ : Use  $R_N$  to limit the input frequency to the  $P_0$  divider to  $\leq 250 MHz$ .

- 3. Maximum  $M_1$  input frequency is: 1GHz for  $M_1 = \div 1... \div 7$  and 4GHz for  $M_1 > \div 7$

- 4. Maximum  $M_2$  input frequency is: 1GHz for  $M_2 = \div 1... \div 7$  and 4GHz for  $M_2 > \div 7$

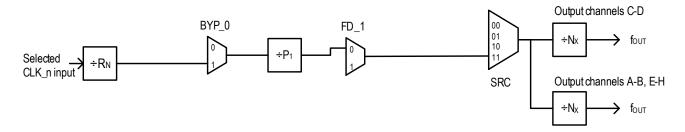

#### 4.2.1.2 Frequency Synthesizer Mode

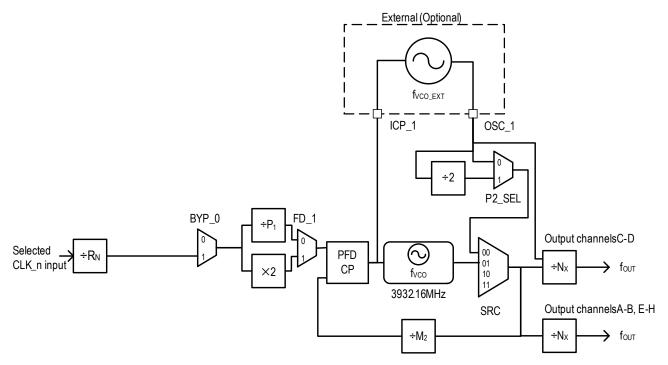

The application for the frequency mode is frequency generation by PLL-1. PLL-0 is bypassed by setting BYP\_0 = 1. It is not required to fit an external VCXO in this mode. PLL-1 can use the internal VCO or an external VCO. The dividers of PLL-1 must be configured to achieve frequency lock to the selected clock input. Figure 5 displays a detailed circuit and Table 4 shows the available frequency dividers for this mode.

Figure 5. Frequency Synthesizer Mode

| Divider                                                  | Range                                                             | Operation for f <sub>VCO</sub> = 3932.16MHz <sup>[1]</sup>                                          |

|----------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Input Divider R <sub>N</sub>                             | ÷1, ÷2, ÷4, ÷8                                                    | Input clock frequency:                                                                              |

| PLL-1 Pre-Divider P <sub>1</sub>                         | ÷1÷127: (7 bit)                                                   | $f_{CLK} = f_{VCO} \times \frac{R_N \times P_1}{M_2}$                                               |

| Frequency Doubler                                        | FD_1 = ×1 or ×2                                                   | CLK VCO M <sub>2</sub>                                                                              |

| PLL-2 Feedback Dividers M <sub>2</sub>                   | ÷8÷1,023: (10 bit)                                                | $P_1$ : Set $P_1$ to 0.5 in above equation if the frequency doubler is engaged by setting FD_1 = 1. |

| Output Divider $N_x$<br>( $x = A, B, C, D, E, F, G, H$ ) | ÷1÷20,480<br>N = {1,2,3,4,5} × 2 <sup>m</sup> with m = 0<br>to 12 | Output (clock or SYSREF) frequency: $f_{OUT} = \frac{f_{VCO}}{N_X}$                                 |

Table 4. Frequency Synthesizer Mode Settings and Divider Values

#### 4.2.1.3 VCXO-PLL Mode

Application for the VCXO-PLL mode is input clock jitter attenuation without the use of PLL-1 for additional frequency generation. Set SRC[1:0] = 10 to bypass PLL-1. PLL-0 must use an external VCXO. The frequency of the VCXO component determines the highest frequency that can be generated at the outputs. The PLL-0 dividers  $P_0$  and  $M_0$  must be configured to achieve frequency lock. For VCXO frequencies higher than 250MHz, set  $P_0$  SEL = 1 to select an additional divide-by-2 in the PLL-0 feedback path. Figure 6 displays a detailed circuit and Table 5 shows the available frequency dividers for this mode.

Figure 6. VCXO-PLL Mode

Table 5. VCXO-PLL (PLL-0) Mode Settings and Divider Values

| Divider                                                       | Range                                                             | Operation (no VCO)                                                                                                        |

|---------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Input Divider R <sub>N</sub>                                  | ÷1, ÷2, ÷4, ÷8                                                    | Input clock frequency (f <sub>VCXO</sub> ≤250MHz):                                                                        |

| PLL-0 Pre-Divider P <sub>0</sub>                              | ÷1÷32,767: (15 bit)                                               | $f_{CLK} = R_{N} \times P_{0} \times \frac{f_{VCXO}}{M_{0}}$                                                              |

| PLL-0 Feedback Divider M <sub>0</sub>                         | ÷1÷32,767: (15 bit)                                               | P3_SEL: Set to 1 for VCXO frequencies higher than 250MHz: $f_{CLK} = R_N \times P_0 \times \frac{f_{VCXO}}{2 \times M_0}$ |

| Output Divider N <sub>x</sub><br>(x = A, B, C, D, E, F, G, H) | ÷1÷20,480<br>N = {1,2,3,4,5} × 2 <sup>m</sup> with m = 0<br>to 12 | Output frequency: $f_{OUT} = \frac{f_{VCXO}}{N_{X}}$                                                                      |

<sup>1.</sup> External VCO operation: use the frequency of the external VCO for f<sub>VCO</sub> in above equations. For external VCO frequencies greater than 4GHz, set PS\_SEL to select the ÷2 path to reduce the external VCO frequency and enter f<sub>VCO</sub>÷2 as VCO frequency in above equations.

#### 4.2.1.4 PLL Bypass (Fanout Buffer/Frequency Divider) Mode

Application for the buffer/divider mode is the fanout of the input signal with optional frequency division. PLL-0 and PLL-1 are not used in this mode, thus frequency multiplication, input jitter attenuation, automatic input switching, PLL lock and input loss detection are not available. Inputs must be selected manually by using the SEL[1:0] register bits. Set BYP\_0 to 1, FD\_1 = 0 and SRC = 11. The dividers  $R_N$ ,  $P_1$  and the output dividers frequency divide the input frequency, the three dividers can be set to a value of  $\div 1$  to replicate the input frequency at the outputs.

The highest frequency that this mode supports is limited to the maximum input frequency (2GHz). Figure 7 displays a detailed circuit and Table 7 shows the available frequency dividers for this mode. The output divider  $N_x$  can be used to divide the input frequency to lower output frequencies (it is recommended to use  $R_N = \div 1$  and  $P_1 = \div 1$ ). The delay circuits use a delay unit controlled by the clock signal frequency at the SRC multiplexer.

Figure 7. PLL Bypass Mode

Table 6. PLL Bypass (Fanout Buffer/Frequency Divider) Mode

| Divider                                                  | Range                                                             | Operation (no VCO)                                    |

|----------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|

| Input Divider R <sub>N</sub>                             | ÷1, ÷2, ÷4, ÷8                                                    | Output frequency:                                     |

| PLL-1 Pre-Divider P <sub>1</sub>                         | ÷1÷127: (7 bit)                                                   | $f_{OUT} = \frac{f_{CLK}}{R_N \times P_1 \times N_x}$ |

| Output Divider $N_x$<br>( $x = A, B, C, D, E, F, G, H$ ) | ÷1÷20,480<br>N = {1,2,3,4,5} × 2 <sup>m</sup> with m = 0<br>to 12 | N ^ 1 ^ N <sub>x</sub>                                |

### 4.2.2 PLL Description

#### 4.2.2.1 VCXO-PLL (PLL-0)

The FBSEL\_PLL\_0 register bit controls the routing of the VCXO-PLL feedback path applicable in dual PLL mode. PLL feedback is routed through the  $M_0$  divider; alternatively, the feedback path is routed through the second PLL and both the  $M_0$  and  $M_1$  feedback divider. The recommended feedback path for achieving deterministic phase delay from the clock input to the outputs is the path through both the  $M_0$  and  $M_1$ , in combination with the divider setting  $P_1 = \div 1$ . The pre-dividers  $R_N$  and  $P_0$ , and the feedback dividers  $M_0$  and  $M_1$ , require configuration to match the input frequency to the VCXO-frequency.  $M_0$  has a divider value range of 15 bits;  $M_1$  has 14 bits. Multiple divider settings are available to enable support for input frequencies of e.g. 245.76, 122.88, 61.44 and 30.72MHz and the VCXO-frequencies of 122.88MHz, 61.44, 38.4, 30.72, 245.76 and 491.52MHz. In addition, the range of available input and feedback dividers allows to adjust the phase detector frequency independent on the input and VCXO frequencies.

The PLL-0 charge pump is configurable via the I\_CP0, I\_CP0\_SINK\_EN, and I\_ICP0\_OFFSET registers. The charge pump current can be set in the range up to 3mA in 100 or 200µA steps. At startup, the VCXO control voltage at the ICP\_0 pin is held at 50% of the VDD33\_CP0 voltage level (1.65V) to center the VCXO frequency (FCV0 = 1). After startup, the user must set the FVC\_0 control bit to 0 to enable VCXO-PLL lock. Input clock switching and holdover functions require the use of the VCXO-PLL in the active signal path.

Low input frequency configurations: If the input frequency after the divider  $R_N$  is lower than the output of the  $M_1$  divider, then the user must set the "BLOCK\_LOR" register bit to 1 in order for PLL-0 to operate correctly. In this condition, the LOS (Loss of input signal) function is not valid, also preventing the automatic input switching function of the device.

In frequency synthesizer mode, PLL-0 is not used and holdover functions are not available.

Table 7. PLL-0 Example Configurations for  $f_{VCXO}$  = 122.88MHz<sup>[1]</sup>

| Input Frequency |                | PLL-0 Divider Settings |                |                           |  |  |

|-----------------|----------------|------------------------|----------------|---------------------------|--|--|

| (MHz)           | R <sub>N</sub> | P <sub>0</sub>         | M <sub>0</sub> | f <sub>PFD</sub><br>(MHz) |  |  |

| 245.76          | 1              | 2                      | 1              | 122.88                    |  |  |

|                 | 1              | 32                     | 16             | 7.68                      |  |  |

|                 | 1              | 256                    | 128            | 0.96                      |  |  |

|                 | 1              | 2048                   | 1024           | 0.12                      |  |  |

| 122.88          | 1              | 1                      | 1              | 122.88                    |  |  |

|                 | 1              | 16                     | 16             | 7.68                      |  |  |

|                 | 1              | 128                    | 128            | 0.96                      |  |  |

|                 | 1              | 1024                   | 1024           | 0.12                      |  |  |

| 1966.08         | 8              | 2                      | 1              | 122.88                    |  |  |

<sup>1.</sup> BYP\_1=0

#### 4.2.2.2 PLL Feedback Path

PLL-0 uses  $M_0$  or  $M_0 \times M_1$ ; PLL-1 uses  $M_2$  as the feedback divider. Configuring the feedback path through the  $M_0$  and  $M_1$  dividers enables deterministic delay from the input to the outputs (for more information, see Table 8).

Table 8. VCXO-PLL (PLL-0) Feedback Path Settings

| FBSEL_PLL_0 | Operation                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | Independent PLL feedback.  PLL-0 feedback path through the $M_0$ divider (and through an additional $\div 2$ if P3_SEL = 1)  PLL-1 feedback path uses the $M_2$ divider.                                     |

| 1           | Recommended feedback configuration for achieving deterministic delay from input to the outputs.<br>PLL-0 feedback path through the $M_1 \times M_0$ dividers.<br>PLL-1 feedback path uses the $M_2$ divider. |

#### 4.2.2.3 PLL-1

PLL-1 is a high-frequency synthesizer. This PLL locks to the output signal of PLL-0 in dual PLL mode or to the input frequency in frequency synthesis mode. PLL-1 uses the internal VCO (3932.16MHz) or an external VCO at any frequency from 700MHz to 6GHz. Achieving PLL lock requires the configuration of FD\_1 (frequency doubler) or  $P_1$  (pre-divider), and the feedback divider  $M_2$  to match the input and feedback frequency at the phase detector. These settings may change depending on the actual VCO and input frequencies. If the external VCO frequency  $f_{VCO}$  is greater than 4GHz, set  $P_2$ SEL to 1 to select the path through the divider  $\div 2$ . The effective VCO frequency routed to the PLL-1 feedback divider, output divider, and SYSREF generator is then  $f_{VCO} \div 2$ . The  $P_2$ SEL setting also impacts the reference frequency for the delay circuits: the frequency at the SRC multiplexer output is the reference frequency for all digital delay circuits. The  $M_2$  feedback divider in PLL-1 is integer. The PLL-1 charge pump is configurable via the  $I_2$ CP1,  $I_2$ CP1\_SINK\_EN, and  $I_2$ CP1\_OFFSET registers. The charge pump current can be set in the range up to 3mA in 100 or 200µA steps.

This PLL is internally configured to high-bandwidth. Best phase noise is typically achieved by engaging the internal frequency doubler (FD\_1 = 1,  $\times$ 2). If engaged, the input signal to PLL-1 is first doubled in frequency, increasing the phase detector frequency of PLL-1. Enabling the frequency doubler disables the frequency pre-divider P<sub>1</sub>. If the frequency doubler is not used (FD\_1 = 0), the P<sub>1</sub> pre-divider has to be configured. Typically P<sub>1</sub> is set to  $\div$ 1 to keep the phase detector frequency as high as possible. Set P<sub>1</sub> to other divider values to achieve specific frequency ratios (1 to 19.2, 1 to 76.8, etc.) between the first and second PLL.

Table 9. PLL-1 Mode

| Description                 | RF_PLL Operation <sup>[1]</sup> | M <sub>2</sub> Registers |

|-----------------------------|---------------------------------|--------------------------|

| Integer frequency synthesis | $f_{VCO} = f_{PFD_1} \times M2$ | 0x2C - 0x2D              |

f<sub>PFD\_1</sub> is the phase detector frequency of PLL-1. In dual PLL mode, f<sub>PFD\_1</sub> is the output frequency of PLL-0 divided by P<sub>1</sub> or multiplied by 2.

**Table 10. Frequency Doubler**

| FD_1 | Operation                                                                                                            |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0    | Frequency doubler off (×1). P <sub>1</sub> divides the PLL-1 input signal                                            |  |  |  |  |

| 1    | Frequency doubler on (×2). The PLL-1 input signal is doubled in frequency. The P <sub>1</sub> divider has no effect. |  |  |  |  |

Table 11. Example PLL-1 Configuration

| PLL-1 Input-       |      | PLL-1          |                |                           |  |  |  |

|--------------------|------|----------------|----------------|---------------------------|--|--|--|

| Frequency<br>(MHz) | FD_1 | P <sub>1</sub> | M <sub>2</sub> | f <sub>VCO</sub><br>(MHz) |  |  |  |

| 122.88             | ×2   | _              | 16             | 3932.16                   |  |  |  |

| 245.76             | ×2   | _              | 8              | 3932.16                   |  |  |  |

| 245.76             | ×1   | 1              | 16             | 3932.16                   |  |  |  |

| 491.52             | ×1   | 1              | 8              | 3932.16                   |  |  |  |

| 491.52             | ×1   | 2              | 12             | 5898.24 (external)        |  |  |  |

#### 4.2.3 PLL-0 (VCXO-PLL) Lock Detect

The PLL-0 lock detect circuit uses the signal phase difference at the phase detector as lock criteria; the phase detector is fed by the output signals of the  $M_0$  and  $P_0$  dividers. PLL lock is reported when the phase difference between both signals into the PLL-0 phase detector is lower than or equal to the phase difference set by LOCK\_TH[14:0] for more than the number clock cycles (of the  $M_0$  divider output) set by LOCK\_GOOD\_COUNT[1:0]. PLL-0 lock state is reported through the ST\_PLL0\_LOCK (momentary) and LS\_PLL0\_LOCK (sticky, resettable) status bits (for status bit functions, see Table 25). PLL lock can be reported by a GPIO pin. Loss-of-lock can also be signaled as interrupt signal via a GPIO pin.

The PLL-0 lock detect function is available in dual PLL and VCXO-PLL (PLL-0 only) mode. The divider  $M_0$  is used as frequency divider for the comparison signal. The  $M_0$  divider must be set to a value equal to or greater than  $\div 4$  for lock detect to work correctly.

A static clock input is detected as PLL loss of lock. PLL-0 lock detect is not available in PLL bypass (fanout buffer) mode or in configurations that do not feed a clock signal to the frequency divider  $M_0$ . The maximum input frequency to the  $M_0$  and  $P_0$  dividers is 250MHz. For higher input frequencies than 250MHz, use the  $R_N$  divider to divide the frequency down to  $\leq$  250MHz. The lock detect circuits works for the input frequencies that achieve PLL-0 lock. Setting the FVC\_0 register bit will unlock PLL-0 and identifies this as a loss of lock condition. Entering holdover also reports a PLL-0 loss of lock.

#### 4.2.4 PLL-1 Lock Detect

PLL-1 lock detect evaluates the calibration state machine status flag for completion and compares the PLL-1 loop filter voltage to a voltage range (window). PLL-1 lock is signaled through the ST\_PLL1\_LOCK (momentary) and LS\_PLL1\_LOCK (sticky, resettable) status bits (see Table 25). Lock status can be reported as a hardware signal through the GPIO\_[1:0] pin interface.

A static clock input to PLL-1 is detected as loss of lock. The PLL-1 lock detect function is available in dual PLL and synthesizer mode (PLL-1). PLL-1 lock detect works up to the specified PLL-1 phase detector frequency (500MHz) and over the entire frequency range PLL-1 lock range. PLL-1 lock detect is not supported in configurations that do not use PLL-1. Lock detect is also available in PLL synthesizer mode with an external VCO.

## 4.3 Output Channel and JESD204B/C Logic

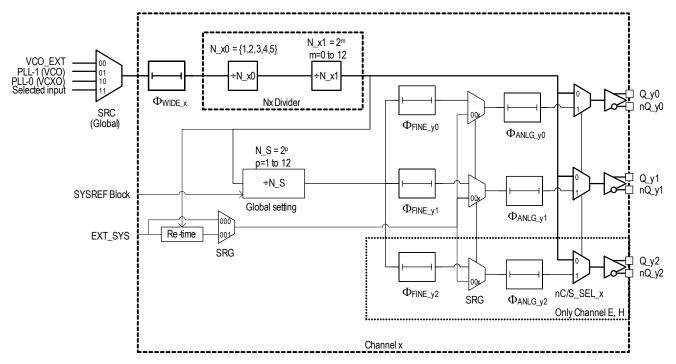

## 4.3.1 Channel Description

The 8V19N880 has eight output channels with a total of 18 differential channels plus one VCXO output channel. Six channels (A, B, C, D, F, G) support two differential outputs and two channels (E, H) support three differential outputs. The outputs of channels C and D support output frequencies up to 6GHz and require a 3.3V output supply. Channels A, B, E, F, G, and H are supplied by 1.8V and support output frequencies up to 4GHz. Each channel can be configured as a clock channel or as a SYSREF channel by using the respective nC/S\_SEL\_x multiplexer register bit. The clock/SYSREF configuration applies to all outputs of a channel.

| Channel    | Number of<br>Outputs | Output Signals                                                                          | Output Supply<br>Voltage | Diagram  |

|------------|----------------------|-----------------------------------------------------------------------------------------|--------------------------|----------|

| A, B, F, G | 2                    | Clock ≤ 4GHz (from PLL-1) or     SYSREF                                                 | 1.8V                     | Figure 8 |

| E, H       | 3                    | Clock ≤ 4GHz (from PLL-1) or     SYSREF                                                 | 1.8V                     | Figure 8 |

| C, D       | 2                    | Clock ≤ 6GHz (directly from OSC_1 input) or     Clock ≤ 4GHz (from PLL-1) or     SYSREF | 3.3V                     | Figure 9 |

**Table 12. Output Channel Description**

#### 4.3.1.1 Clock/SYSREF Channels A, B, E, F, G, H

The channels A, B, E, F, G, and H can operate as a device clock or as a SYSREF channel, controlled by the nC/S\_SEL\_x selector (for information, see Figure 8).

#### 4.3.1.1.1 Clock Operation

A channel configured to clock operation (nC/S\_SEL\_x = 0) contains a two-stage frequency divider  $N_x$  and one digital phase delay circuit  $\Phi_{\text{WIDE}\_x}$ . Frequency and phase settings are applied to all outputs of a channel. The purpose of the  $N_x$  divider is frequency generation from the selected frequency source (SRC multiplexer).  $N_x$  can be set to a range of discrete values from  $\div 1$  to  $\div 20,480$ .  $N_x$  is a composite divider consisting of two serial dividers  $N_x = N_x =$

#### 4.3.1.1.2 SYSREF Operation

A channel configured to clock operation (nC/S\_SEL\_x = 1) participates in the central SYSREF pulse/frequency generation. The clock divider  $N_x$  divides the selected source signal to the SYSREF frequency. Similar to clock

operation, the frequency is applied to all outputs of that channel.  $N_x$  can be set to a range of discrete values from  $\div 1$  to  $\div 83,886,080$ .  $N_x$  consists of three serial dividers  $N_x$ 0,  $N_x$ 1, and  $N_x$ 5:  $N_x$ 1 =  $N_x$ 0 ×  $N_x$ 1 ×  $N_x$ 5. For example, setting  $N_x$ 0 to  $\div 2$ ,  $N_x$ 1 to  $\div 8$ , and  $N_x$ 5 to  $\div 32$  will result in a SYSREF frequency divider of  $N_x$ 1 =  $\div 512$ . This example divider value generates a SYSREF output frequency of 7.68MHz if the internal VCO is used. A  $N_x$ 5 divider physically exists in each channel, however, all  $N_x$ 5 dividers share the same global setting ( $N_x$ 6 in register 0x38). For phase delay, a SYSREF channel contains the circuits  $\Phi_{WIDE_x}$ 9,  $\Phi_{FINE_y}$ 9, and  $\Phi_{ANLG_y}$ 9. Similar to a clock channel,  $\Phi_{WIDE_x}$ 9 phase settings are applied to all channel outputs. Each output can use the additional delay circuits  $\Phi_{FINE_y}$ 9 and  $\Phi_{ANLG_y}$ 9 for output-to-output fine phase alignment. These output delay circuits are unavailable when the channel is configured to clock operation.

#### 4.3.1.1.3 Synchronization of Clock and SYSREF Channels

The device can synchronize the phase of clock and SYSREF outputs across channels. For synchronization, rules apply for the selection of N\_x0 and N\_x1 dividers. In a SYSREF channel, the input frequency to the N\_S divider block must be set to a common divisor of the frequencies of the clock channels. For example, channels A, B, and E are configured as clock channel with the output frequencies of 122.88MHz (channel A, N = 32), 245.76 MHz (channel B, N = 16) and 983.04MHz (channel E, N = 4); channel F is configured to SYSREF at 7.68MHz. A common divisor of the three clock frequencies in channels A, B, and E is 122.88MHz. This divisor is calculated by dividing the VCO frequency by the lowest common multiple clock frequency divider: 3932.16MHz ÷ LCM(32, 16, 4). In the SYSREF channel, the input to the N\_S divider must now be configured to 122.88MHz (by setting N\_x0 × N\_x1 to ÷32: the VCO frequency of 3932.16MHz is divided by 32). The SYSREF divider N\_S is then configured to 16 to achieve 7.68MHz at the channel F outputs. Failure to set the SYSREF channel divider to a common frequency of the clock channels may result in the SYSREF outputs not being synchronous to clock outputs.

Figure 8. Output Channels A, B, E, F, G, and H

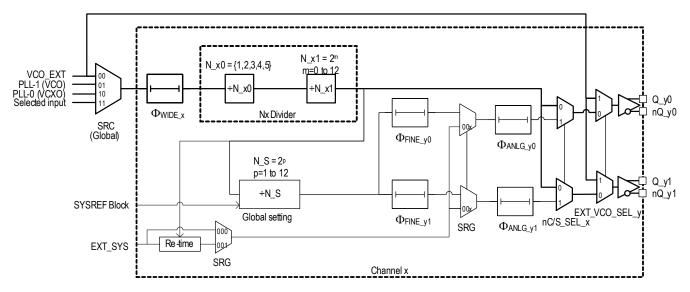

#### 4.3.1.2 6GHz RF Clock/SYSREF Channels C, D

The two RF clock channels C and D buffer the external oscillator signal (VCO\_EXT) up to an output frequency of 6GHz (see Figure 9). Alternatively, the channels C and D operate as device clock/SYSREF signal channel as described in Clock/SYSREF Channels A, B, E, F, G, H where the frequency source is PLL-0 or PLL-1 (internal VCO). In the alternative mode, the maximum output frequency is 4GHz. For channels C and D, the output supply voltage is  $V_{DDO33\ V} = 3.3V$ .

Figure 9. RF Output Channels C, D (Two Outputs)

### 4.3.2 Clock Delay Circuits

The purpose of the phase delay circuits is to establish a desired phase relationship between the selected input and any output, and across outputs (see Table 13). In JESD204B/C applications, the delay circuits establish phase offsets between SYSREF signals and their corresponding device clocks. The phase delay circuits  $\Phi_{FB}$ ,  $\Phi_{WIDE}$  <sub>x</sub>, and  $\Phi_{FINE}$  <sub>v</sub> (for SYSREF) are a function of the source frequency at the output of the SRC multiplexer.

If the *internal VCO* (3932.16MHz) is the channel signal source: the delay step size is selectable 127ps (one-half VCO cycle, channel delay) or 254ps (one VCO cycle, SYSREF delay). If an *external VCO* or *external VCXO* is the signal source: the frequency at the SRC multiplexer determines the delay units. External VCO frequencies of greater than 4GHz have to be divided by 2 (by using P2\_SEL = 1). The  $\Phi_{ANLG_y}$  circuits are implemented by gate delays and have a very small delay step size of approximately 30ps, independent of any internal or external VCO reference frequency.

The phase delay circuits  $\Phi_{WIDE\_x}$  have a wide range and can be used for coarse clock and SYSREF signal phase alignments. The delay circuits  $\Phi_{FINE\_y0}$  and  $\Phi_{ANLG\_y0}$ ;  $\Phi_{FINE\_y1}$  and  $\Phi_{ANLG\_y1}$  are available in SYSREF channels and have a short range and finer resolution for use in board signal de-skewing and the exact placement of a SYSREF signal edge to the rising edge of a clock signal. Changing the setting of the delay circuit  $\Phi_{FINE\_y0}$  and  $\Phi_{ANLG\_y0}$ ;  $\Phi_{FINE\_y1}$  and  $\Phi_{ANLG\_y1}$  will not result in output voltage transients, gaps, or runt pulses so that delay setting changes during device operation are supported.

| Delay Circuit                        | Unit <sup>[1]</sup>                  | Steps            | Range (ns)   | Use for Alignment                                                                                  |

|--------------------------------------|--------------------------------------|------------------|--------------|----------------------------------------------------------------------------------------------------|

| PLL-0 Feedback Clock Φ <sub>FB</sub> | $\frac{1}{f_{VCO}} = 254ps$          | 4096<br>(12 bit) | 0 – 1,041.41 | Input to output (incident edge) alignment.                                                         |

| Channel Clock Φ <sub>WIDE_x</sub>    | $\frac{1}{2 \times f_{VCO}} = 127ps$ | 512<br>(9 bit)   | 0 – 64.977   | Incident rising clock edges are aligned, independent on the divider N <sub>x</sub> across channels |

**Table 13. Delay Circuit Settings**

Table 13. Delay Circuit Settings (Cont.)

| Delay Circuit                                                                            | Unit <sup>[1]</sup>                                                    | Steps        | Range (ns)                   | Use for Alignment                                                                                                                  |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Output SYSREF $\Phi_{\text{FINE\_y0}}$ $\Phi_{\text{FINE\_y1}}$ $\Phi_{\text{FINE\_y2}}$ | f <sub>VCO</sub> ≥ 2GHz and internal VCO: $\frac{1}{f_{VCO}} = 254 ps$ | 4<br>(2 bit) | 0 – 0.763                    | Output-to-output in channel and across channels, clock to SYSREF alignment.  Can be powered down for lowest noise floor operation. |

|                                                                                          | $f_{VCO} < 2GHz^{[2]}$ : $\frac{1}{2 \times f_{VCO}}$                  |              | 0 – 3 ÷ (2f <sub>VCO</sub> ) |                                                                                                                                    |

| Output SYSREF $\Phi_{ANLG\_y0}$ $\Phi_{ANLG\_y1}$ $\Phi_{ANLG\_y2}$                      | 30ps (analog)                                                          | 8<br>(3 bit) | 0 – 0.210                    |                                                                                                                                    |

<sup>1.</sup> Table is valid for using the internal VCO at a frequency of 3932.16MHz. For an external VCO, replace  $f_{VCO}$  by the actual VCO frequency or VCO frequency ÷ 2 if greater than 4GHz. Examples: external VCO of 2949.12MHz:  $\Phi_{WIDE\_x}$  is 169ps (P2\_SEL = 0). External VCO of 5898.24MHz:  $\Phi_{WIDE\_x}$  is also 169ps (P2\_SEL = 1, external VCO is pre-divided).

<sup>2.</sup> When using an external VCO at frequencies < 2GHz, the output SYSREF delay unit can be selected: 1/f<sub>VCO</sub> and 1/2f<sub>VCO</sub>. See RETIME\_DIV\_x function.

## 4.3.3 Differential Outputs

**Table 14. Output Features**

| Outputs            | Description        | Config.                                 | Source                                  | Supply<br>Voltag<br>e | Style  | Termination <sup>[1]</sup>    | Ampl. <sup>[2]</sup> <sup>[3]</sup> (mV) | Disabl<br>e | Power<br>Down |

|--------------------|--------------------|-----------------------------------------|-----------------------------------------|-----------------------|--------|-------------------------------|------------------------------------------|-------------|---------------|

| Q_C0-1,<br>Q_D0-1  | Clock ≤<br>6GHz    | EXT_VCO_SEL_<br>y = 1                   | OSC_1                                   | 3.3V                  | LVPECL | $50\Omega$ to V <sub>TT</sub> | 300, 400,<br>550, 700                    | Y           | Y             |

|                    | Clock ≤<br>4GHz    | EXT_VCO_SEL_<br>y = 0<br>nC/S_SEL_x = 0 | PLL-0,<br>PLL-1 or<br>selected<br>input | 3.3V                  | LVPECL | $50\Omega$ to V <sub>TT</sub> | 300, 400,<br>550, 700                    |             |               |

|                    | SYSREF             | EXT_VCO_SEL_<br>y = 0<br>nC/S_SEL_x = 1 | SYSREF<br>Generato<br>r                 | 3.3V                  | LVPECL | 50Ω to $V_{TT}$               | 300, 400,<br>550, 700                    | Y           | Y             |

| Q_A0-1,<br>Q_B0-1, | Clock ≤<br>4GHz    | nC/S_SEL_x = 0                          | PLL-0,<br>PLL-1 or                      | 1.8V                  | LVPECL | 50Ω to $V_{TT}$               | 300, 400,<br>550, 700                    | Y           | Y             |

| Q_E0-2,<br>Q_F0-1, |                    |                                         | selected<br>input                       |                       | LVDS   | 100Ω<br>differential          | 350, 500,<br>line bias                   |             |               |

| Q_G0-1,<br>Q_H0-2  | SYSREF             | nC/S_SEL_x = 1                          | SYSREF<br>Generato                      | 1.8V                  | LVPECL | $50\Omega$ to V <sub>TT</sub> | 300, 400,<br>550, 700                    | Y           | Y             |

|                    |                    |                                         | r                                       |                       | LVDS   | 100Ω<br>differential          | 350, 500,<br>line bias                   | Y           | Y             |

| Q_VCX              | PLL-0              | -                                       | PLL-0                                   | 1.8V                  | LVPECL | $50\Omega$ to V <sub>TT</sub> | 700                                      | N           | Υ             |

| 0                  | buffered<br>output |                                         |                                         |                       | LVDS   | 100Ω<br>differential          | 350                                      |             |               |

<sup>1.</sup> AC coupling and DC coupling supported.

Table 15. Q\_y Output States in Clock Mode (nC/SEL = 0)[1]

| PD | EN | Output Operation Description                   |  |  |  |

|----|----|------------------------------------------------|--|--|--|

| 0  | 0  | Static low (Q = low, nQ = high) <sup>[2]</sup> |  |  |  |

|    | 1  | Switching (Clock)                              |  |  |  |

| 1  | Х  | Powered down                                   |  |  |  |

<sup>1.</sup> Clock mode: Configuration bits nBIAS\_r, PD\_SYSREF, BIAS\_TYPE, and INV\_SYS have no effect on Q\_y outputs.

<sup>2.</sup> Amplitudes are measured single-endedly.

<sup>3.</sup> See Table 17 for LVPECL termination voltages ( $V_{TT}$ ).

<sup>2.</sup> Output disable operation of Q\_C and Q\_D outputs when outputs are used for an external VCO (EXT\_VCO\_SEL\_y = 1): Q = High and nQ = High.

Table 16. Q\_y Output States in SYSREF Mode (nC/SEL = 1)

| PD_y | EN | nBIAS | PD_SYSRE<br>F | BIAS_TYPE | INV_SYS | Output Operation Description <sup>[1]</sup>                   |

|------|----|-------|---------------|-----------|---------|---------------------------------------------------------------|

| 0    | 0  | Х     | Х             | Х         | Х       | Static low level                                              |

|      | 1  | 0     | 0             | 0         | 0       | Switching (SYSREF)[2]                                         |

|      |    |       |               |           | 1       | Switching (SYSREF inverted)[2]                                |

|      |    |       |               | 1         | 0       | Switching (SYSREF) / crosspoint level <sup>[2]</sup>          |

|      |    |       |               |           | 1       | Switching (SYSREF inverted) / crosspoint level <sup>[2]</sup> |

|      |    |       | 1             | 0         | 0       | SYSREF power down                                             |

|      |    |       |               |           | 1       | Static high level                                             |

|      |    |       |               | 1         | 0       |                                                               |

|      |    |       |               |           | 1       |                                                               |

|      |    | 1     | 0             | 0         | 0       | SYSREF static low level <sup>[2]</sup>                        |

|      |    |       |               |           | 1       |                                                               |

|      |    |       |               | 1         | 0       | SYSREF static crosspoint level <sup>[2]</sup>                 |

|      |    |       |               |           | 1       | -                                                             |

|      |    |       | 1             | 0         | 0       | SYSREF power down                                             |

|      |    |       |               |           | 1       | Static high level                                             |

|      |    |       |               | 1         | 0       | 1                                                             |

|      |    |       |               |           | 1       | 1                                                             |

| 1    | Х  | Х     | Х             | Х         | Х       | Powered down                                                  |

<sup>1.</sup> Level description: Static low: Q = low, nQ = high; Static high: Q = high, nQ = high; Crosspoint: Q and nQ are both at the LVDS crosspoint voltage.

Table 17. LVPECL Termination Voltage,  $\mathbf{V}_{TT}$

| Output Supply Voltage     | Amplitude (mV) | V <sub>TT</sub>                    |

|---------------------------|----------------|------------------------------------|

| V <sub>DDO_V</sub> = 1.8V | 300            | 0.25V (V <sub>DDO_V</sub> - 1.55V) |

|                           | 400            | 0.15V (V <sub>DDO_V</sub> - 1.65V) |

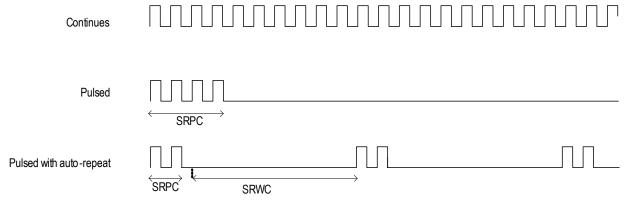

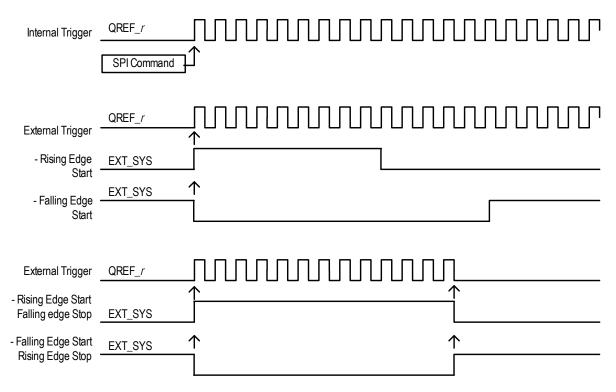

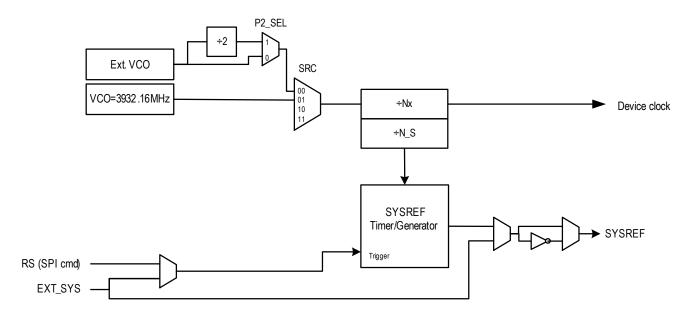

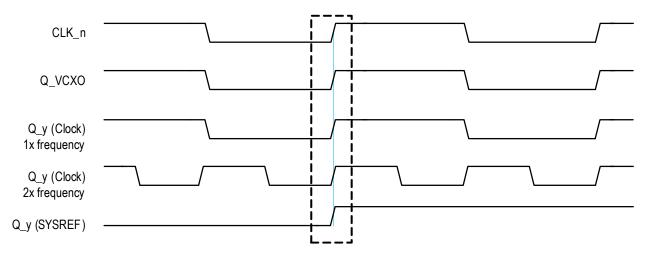

|                           | 550            | GND                                |