# RENESAS

### RAA489206

16-Cell Battery Front End

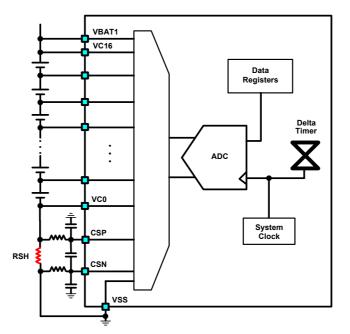

The RAA489206 is a 16-cell Battery Front End (BFE) IC, an essential component of any Battery Management System (BMS) that periodically scans battery status and the operating environment to optimize battery life and prevent catastrophic failures.

To manage the overall state of the battery pack, a differential multiplexer and 16-bit ADC allow for the accurate monitoring of cell voltage, temperature, and load current.

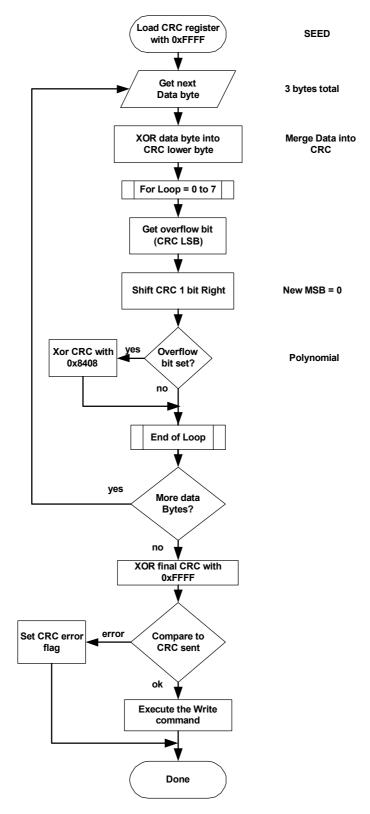

The RAA489206 supports I<sup>2</sup>C, SPI, and SPI w/CRC protocols allowing customers to connect an MCU in a proprietary battery management solution.

Low current consumption with an average IDLE mode current of  $200\mu$ A and a SHIP mode current of less than  $18\mu$ A maximizes the storage and discharge life of a battery pack.

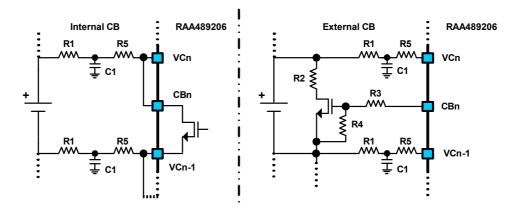

The RAA489206 features internal cell balancing circuitry that provides 8mA of balance current per cell. External cell balancing for higher currents is also supported.

This 16-cell high voltage BFE IC is offered in an efficient 64 Ld QFN package with a thermal pad.

#### Features

- High hot plug rating: 62V

- V<sub>CELL</sub> accuracy: ±10mV

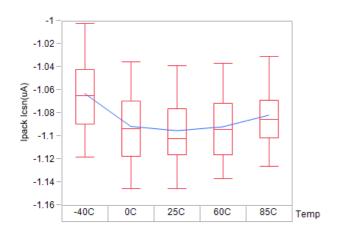

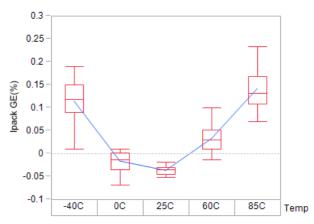

- I<sub>PACK</sub> accuracy: ±0.2%

- 16-bit V<sub>CELL</sub> and I<sub>PACK</sub> measurements

- Charge/Load wakeup detection circuitry

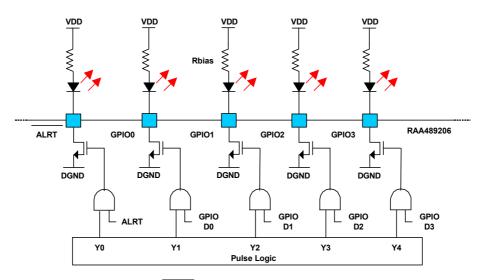

- 4-pin GPIO port

- Integrated 3.3V regulator

- Supports I<sup>2</sup>C, SPI, and SPIw/CRC communications

### Applications

- Light electric vehicles such as e-bikes, e-scooters, and e-motorcycles

- Cordless power and gardening tools

- Home appliances

- 24V, 36V, 42V, and 48V portable battery packs

- Telecom and server farms

- Solar farms

- Energy storage systems

# Contents

| 1. | Over       | view                                                | . 4 |

|----|------------|-----------------------------------------------------|-----|

|    | 1.1<br>1.2 | Typical Application                                 |     |

| 2. | Pin Ir     | nformation                                          | . 6 |

|    | 2.1        | Pin Assignments                                     | . 6 |

|    | 2.2        | Pin Descriptions                                    |     |

| 3. | Spec       | ifications                                          | 9   |

| 0. | 3.1        | Absolute Maximum Ratings                            |     |

|    | 3.1        | Thermal Information                                 |     |

|    | 3.2<br>3.3 | Recommended Operation Conditions                    |     |

|    | 3.4        | Electrical Specifications                           |     |

| 4. |            | al Performance Graphs                               |     |

|    | •••        | •                                                   |     |

| 5. | -          | sters                                               |     |

|    | 5.1        | Device Details                                      |     |

|    | 5.2        | Global Controls                                     |     |

|    | 5.3        | V <sub>CELL</sub> and I <sub>PACK</sub> Measurement |     |

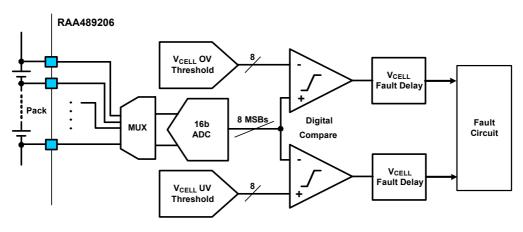

|    | 5.4        | V <sub>CELL</sub> Fault Detectors                   |     |

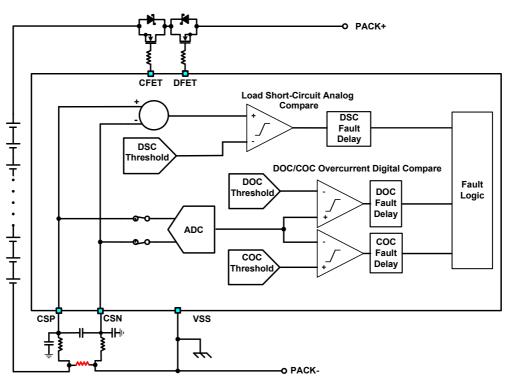

|    | 5.5        | I <sub>PACK</sub> Fault Detectors                   |     |

|    | 5.6        | ETAUX Port                                          |     |

|    | 5.7        | ETAUX Detectors                                     |     |

|    | 5.8        | Internal Temperature                                |     |

|    | 5.9        | Regulator Measurements and Detectors                |     |

|    | 5.10       | V <sub>BAT1</sub>                                   |     |

|    | 5.11       | Power FET Block                                     |     |

|    | 5.12       | Cell Balancing Registers                            |     |

|    | 5.13       | System Faults and Status                            | 78  |

| 6. | Pin F      | unctionality                                        | 88  |

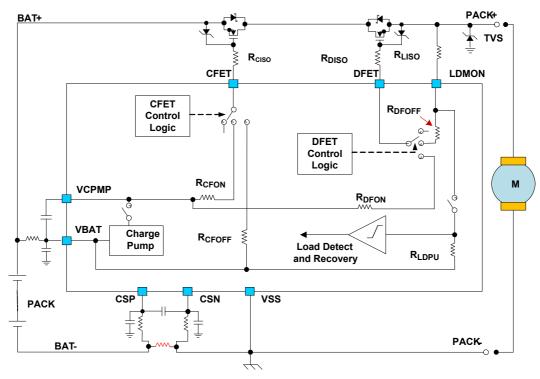

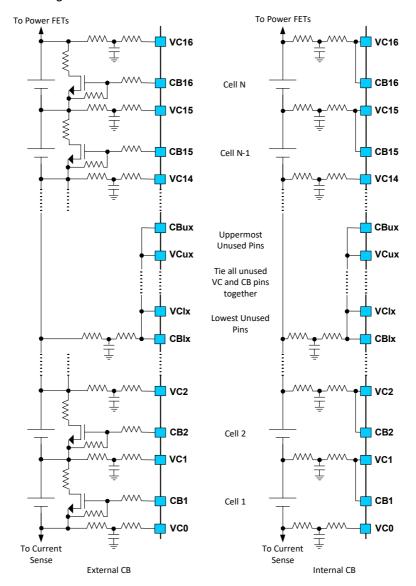

|    | 6.1        | VCn Pins                                            | 88  |

|    | 6.2        | CBn Pins                                            | 89  |

|    | 6.3        | CSP and CSN Pins (24, 25)                           | 90  |

|    | 6.4        | VSS Pin (26)                                        | 91  |

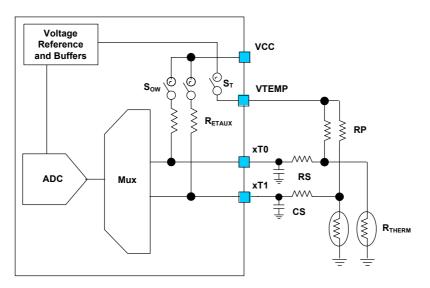

|    | 6.5        | AUX0/xT0, VTEMP, AUX1/xT1 Pins (27, 29, 28)         | 91  |

|    | 6.6        | Regulator and Supply Pins (30-33)                   | 92  |

|    | 6.7        | CMS0 Pin (34)                                       | 93  |

|    | 6.8        | DGND Pins (35,36)                                   | 93  |

|    | 6.9        | V2P5 Pin (37)                                       | 93  |

|    | 6.10       | RESET Pin (38)                                      | 93  |

|    | 6.11       | WAKEUP Pin (39)                                     | 94  |

|    | 6.12       | ALRT Pin (40)                                       | 94  |

|    | 6.13       | ADDR/CS Pin (41)                                    | 94  |

|    | 6.14       | SCL Pin (42)                                        | 94  |

|    | 6.15       | MOSI Pin (43)                                       | 94  |

|    | 6.16       | MISO/SDA Pin (44)                                   | 94  |

|    | 6.17       | GPIO(0-3) Pin (45-48)                               | 95  |

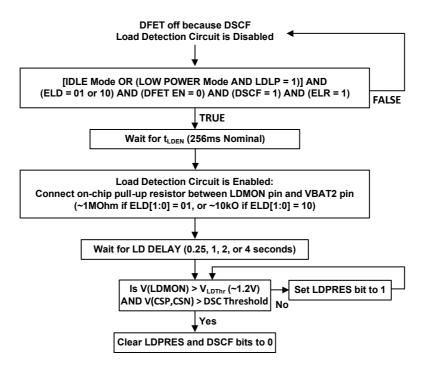

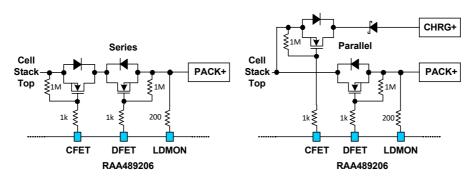

|    | 6.18       | LDMON Pin (49)                                      | 95  |

|     | 6.21  | CFET and DFET Pins (50, 51)       | . 98<br>. 98 |

|-----|-------|-----------------------------------|--------------|

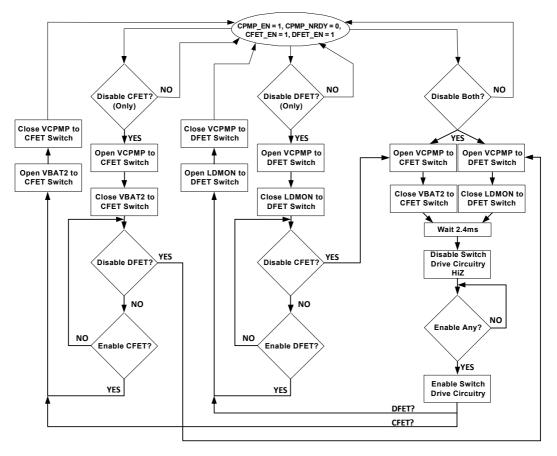

| 7.  |       | •m Operation                      |              |

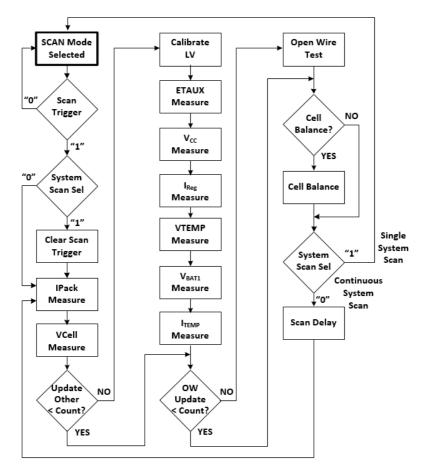

|     | 7.1   | 0x2E Scan Operation               |              |

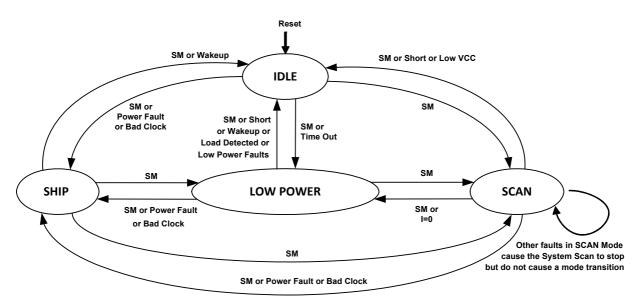

|     | 7.2   | System Modes                      |              |

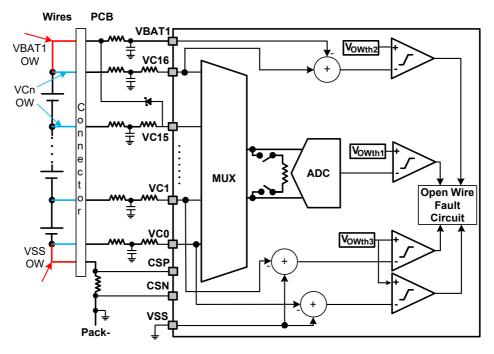

|     | 7.3   | Open-Wire Function                |              |

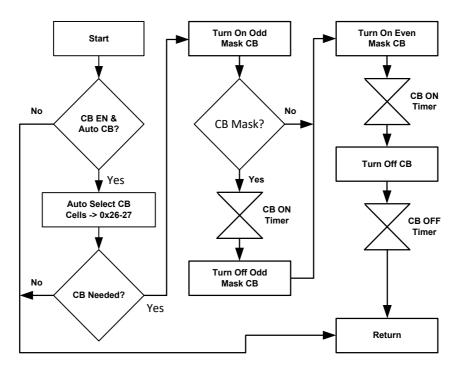

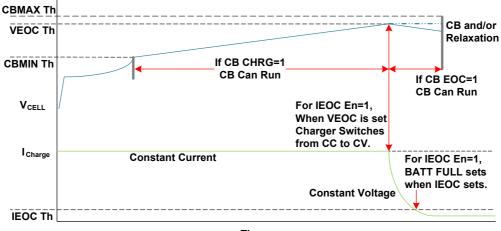

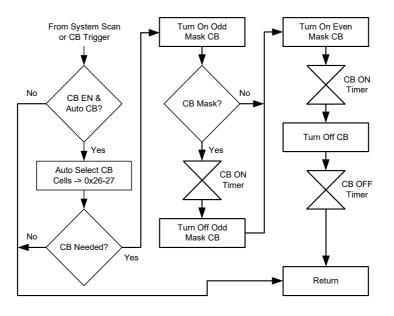

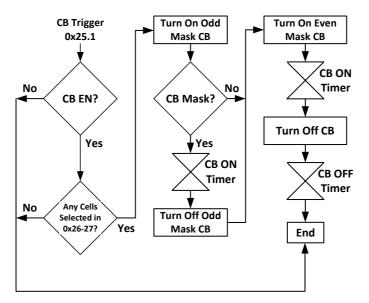

|     | 7.4   | Cell Balancing Examples           | 113          |

|     | 7.5   | Charge Pump                       | 117          |

|     | 7.6   | Trigger Bits                      |              |

| 8.  | Com   | munication Interface              | 119          |

|     | 8.1   | I <sup>2</sup> C Serial Interface | 119          |

|     | 8.2   | SPI Serial Interface              | 123          |

| 9.  | Redu  | ced Cell Count                    | 130          |

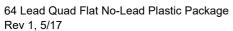

| 10. | Pack  | age Outline Drawing               | 133          |

| 11. | Orde  | ring Information                  | 134          |

| 12. | Revis | sion History                      | 134          |

### 1. Overview

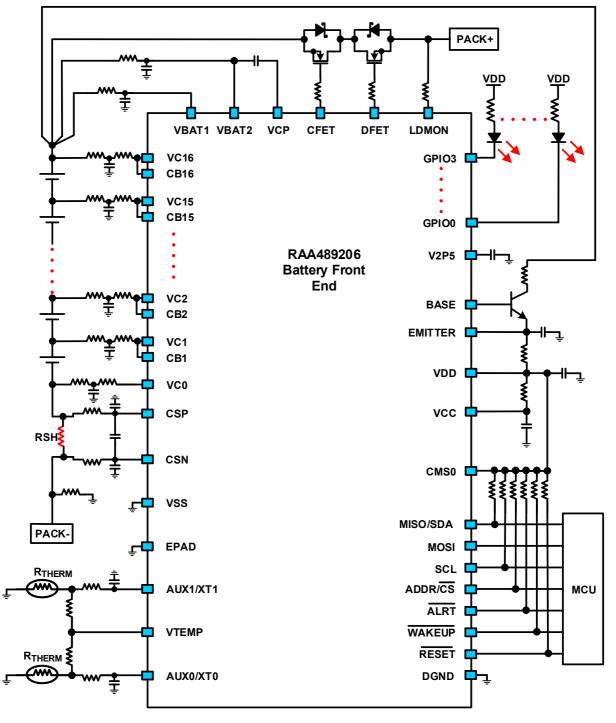

### 1.1 Typical Application

Figure 1. Typical Application

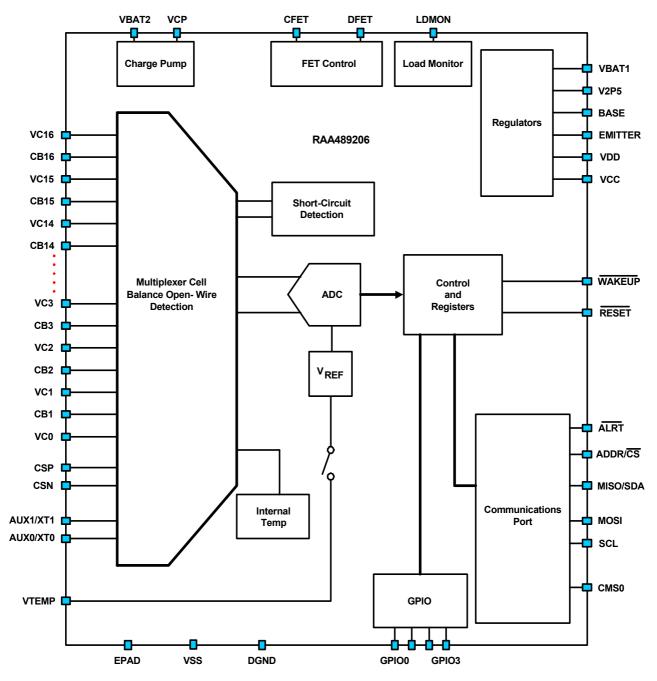

### 1.2 Block Diagram

Figure 2. Block Diagram

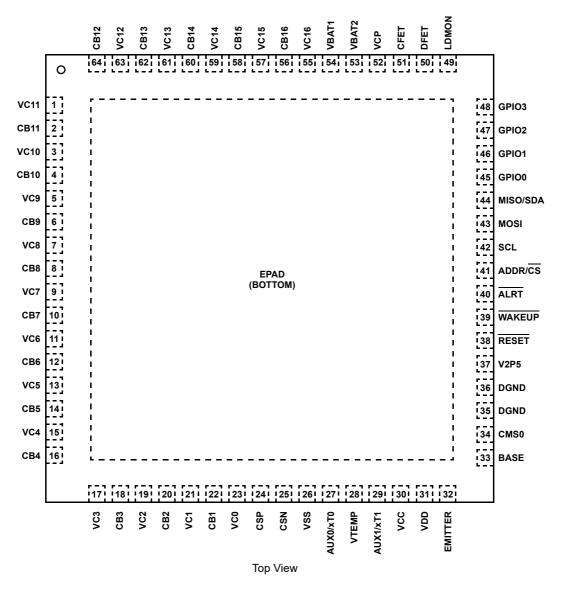

## 2. Pin Information

### 2.1 Pin Assignments

### 2.2 Pin Descriptions

| Pin Number                                                             | Pin Name          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

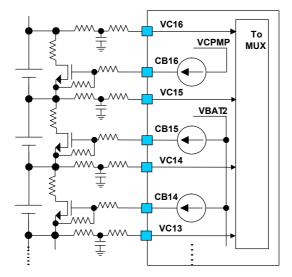

| 1, 3, 5, 7, 9, 11,<br>13, 15, 17, 19,<br>21, 23, 55, 57,<br>59, 61, 63 | VCn (n = 0 to 16) | Battery cell voltage inputs. In an application with a 16-cell battery string, in which cell<br>number 1 connects to the lowest voltage and cell number 16 connects to the highest<br>voltage, VCn connects to the positive terminal of cell n and to the negative terminal of cell<br>n+1 through external resistors (VC16 connects only to the positive terminal of Cell 16, VC0<br>only connects to the negative terminal of Cell 1). For applications with fewer than 16 cells,<br>see Figure 122. |

| 2, 4, 6, 8, 10, 12,<br>14, 16, 18, 20,<br>22, 56, 58, 60,<br>62, 64    | CBn (n = 1 to 16) | Cell balancing pins. When external cell balancing FETs are used, each of these pins controls an external FET. When internal cell balancing FETs are used, these pins connect to the drains of the on-chip cell balancing transistors. See Cell Balancing Registers.                                                                                                                                                                                                                                   |

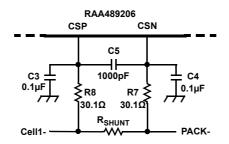

| 24                                                                     | CSP               | Current sense positive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 25         | CSN      | Current sense negative input.                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 26         | VSS      | Analog ground. Connect to the EPAD (electrical/thermal pad under the package).                                                                                                                                                                                                                                                      |  |  |  |  |

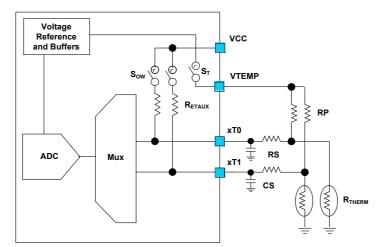

| 27         | AUX0/xT0 | External temperature monitor or general purpose inputs. These inputs are intended for us                                                                                                                                                                                                                                            |  |  |  |  |

| 29         | AUX1/xT1 | with external resistor networks using NTC type thermistor sense elements, but can also b<br>used as general purpose analog inputs at the discretion of the user.                                                                                                                                                                    |  |  |  |  |

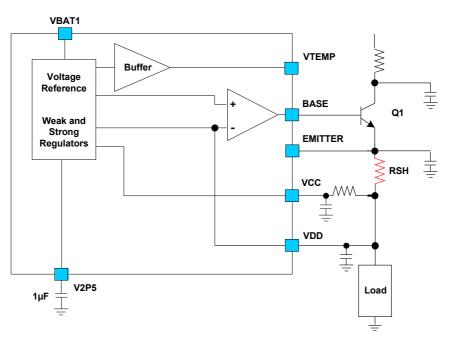

| 28         | VTEMP    | Reference voltage for off-chip temperature monitoring circuit. This is a switched output that supplies a reference voltage to external circuits that include thermistors. It is enabled before starting a measurement of pins AUX0/xT0, AUX1/xT1, or VTEMP itself. It is disconnected from the pin after the measurement completes. |  |  |  |  |

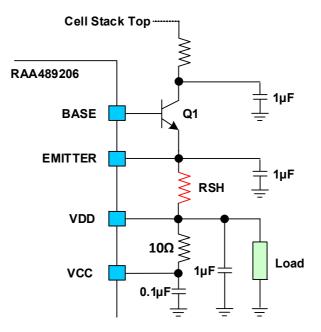

| 30         | VCC      | 3.3V analog supply voltage input. Connect to VDD using a $10\Omega$ resistor and connect a $1\mu$ capacitor between this pin and VSS.                                                                                                                                                                                               |  |  |  |  |

| 31         | VDD      | 3.3V digital supply voltage input. Connect directly or through a current sense resistor to th emitter of the external NPN transistor, connect through a $10\Omega$ resistor to VCC. Connect a $1\mu$ F capacitor between this pin and DGND.                                                                                         |  |  |  |  |

| 32         | EMITTER  | Regulator source current is calculated from the measured voltage between VDD and EMITTER pins. Connect this pin to the Emitter of the external NPN. Connect a regulator current sense resistor between the EMITTER and VDD pins. Connect a 1µF capacitor between this pin and DGND.                                                 |  |  |  |  |

| 33         | BASE     | Regulator control pin. Connect to the base of the external NPN transistor. Do not float.                                                                                                                                                                                                                                            |  |  |  |  |

| 34         | CMS0     | Communication protocol selection. Static input pins; do not change after power-up. See Table 75.                                                                                                                                                                                                                                    |  |  |  |  |

| 35         | DGND     | Digital ground.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 36         | DGND     | 1                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 37         | V2P5     | Internal 2.5V digital supply decoupling pin. Connect a $1\mu$ F capacitor between V2P5 and DGND.                                                                                                                                                                                                                                    |  |  |  |  |

| 38         | RESET    | Active low reset digital input. Connect to a logic HIGH to enable the device. Connect to a logic LOW to reset the device to its Power-On Reset (POR) default state.                                                                                                                                                                 |  |  |  |  |

| 39         | WAKEUP   | Active low wakeup digital input. Connect to a logic LOW voltage level to wake up the device and transition from SHIP or LOW POWER mode to IDLE mode.                                                                                                                                                                                |  |  |  |  |

| 40         | ALRT     | Open-drain, active low alert output. It is asserted under a variety of conditions to interrupt microcontroller. See System Faults and Status.                                                                                                                                                                                       |  |  |  |  |

| 41         | ADDR/CS  | Chip Select input for SPI communication interface or address selection pin for I <sup>2</sup> C communications interface.                                                                                                                                                                                                           |  |  |  |  |

| 42         | SCL      | Serial clock input pin for both SPI and I <sup>2</sup> C communications interfaces.                                                                                                                                                                                                                                                 |  |  |  |  |

| 43         | MOSI     | Master Output Slave Input for SPI communication interface.                                                                                                                                                                                                                                                                          |  |  |  |  |

| 44         | MISO/SDA | Master Input Slave Output for SPI communication interface, or open-drain serial data I/C for I <sup>2</sup> C communication interfaces.                                                                                                                                                                                             |  |  |  |  |

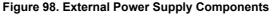

| 45         | GPIO0    | General purpose digital I/Os. Open drain when used as outputs. They can be used as                                                                                                                                                                                                                                                  |  |  |  |  |

| 46         | GPIO1    | <ul> <li>general purpose inputs or outputs, as status LED drivers, or as part of FET driving circuits<br/>See 0x12 - ALRT and GPIO.</li> </ul>                                                                                                                                                                                      |  |  |  |  |

| 47         | GPIO2    |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 48         | GPIO3    |                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

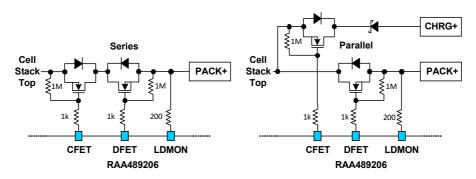

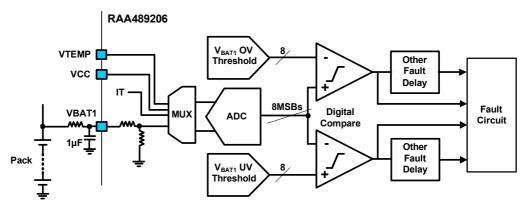

| 49         | LDMON    | Load monitor input. This analog voltage monitor determines whether a normal load, shor<br>or no load is connected to the battery pack. This pin is internally connected to the DFET<br>pin when the DFET is off.                                                                                                                    |  |  |  |  |

| Pin Number | Pin Name | Description                                                                                                                                                                                 |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50         | DFET     | Drives the gate of an external NMOS that controls the current path between the battery pack and the load. This pin is internally connected to the LDMON pin when the DFET is turned off.    |

| 51         | CFET     | Drives the gate of an external NMOS that controls the current path between the battery pack and the charger. This pin is internally connected to the VBAT2 pin when the CFET is turned off. |

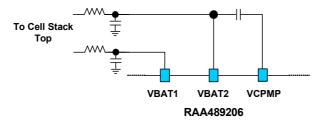

| 52         | VCP      | Charge pump output voltage. Place a capacitor between VCP and VBAT2. The charge pump provides power to FET drivers and part of the cell balancing circuits.                                 |

| 53         | VBAT2    | Power supply pin. Connect to the most positive terminal of the battery pack through dedicated filter. This pin is internally connected to the CFET pin when the CFET is turned off.         |

| 54         | VBAT1    | Power supply pin. Connect to the most positive terminal of the battery pack through dedicated filter.                                                                                       |

| Bottom     | EPAD     | Analog ground. Metal pad under the package. Connect to the VSS pin and ground plane for thermal dissipation.                                                                                |

# 3. Specifications

### 3.1 Absolute Maximum Ratings

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter <sup>[1]</sup>                                                                                                 | Minimum                 | Maximum                | Unit |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|------|

| DGND                                                                                                                     | -0.5                    | +0.5                   | V    |

| CSP, CSN, VC0                                                                                                            | -1.0                    | +1.0                   | V    |

| VBAT1, VBAT2, VCP                                                                                                        | -0.5                    | +70                    | V    |

| VCn (n = 13 to 16)                                                                                                       | -0.5                    | +70                    | V    |

| VCn (n = 9 to 12)                                                                                                        | -0.5                    | +63                    | V    |

| VCn (n = 6 to 8)                                                                                                         | -0.5                    | +54                    | V    |

| VCn (n = 2 to 5)                                                                                                         | -0.5                    | +45                    | V    |

| VC1                                                                                                                      | -0.5                    | +9                     | V    |

| CBn (n = 13 to 16)                                                                                                       | -0.5                    | +70                    | V    |

| CBn (n = 9 to 12)                                                                                                        | -0.5                    | +63                    | V    |

| CBn (n = 6 to 8)                                                                                                         | -0.5                    | +54                    | V    |

| CBn (n = 2 to 5)                                                                                                         | -0.5                    | +45                    | V    |

| CB1                                                                                                                      | -1                      | +9                     | V    |

| CBn [Internal Cell Balancing Current when active] <sup>[2]</sup>                                                         |                         | ±20                    | mA   |

| CFET, DFET, VCP, LDMON <sup>[2]</sup>                                                                                    | -0.5                    | +70                    | V    |

| CFET                                                                                                                     | V <sub>BAT2</sub> - 0.5 | V <sub>BAT2</sub> + 12 | V    |

| DFET                                                                                                                     | LDMON - 0.5             | V <sub>BAT2</sub> + 12 | V    |

| VCP                                                                                                                      | V <sub>BAT2</sub> - 1.0 | V <sub>BAT2</sub> + 12 | V    |

| V2P5 <sup>[2]</sup>                                                                                                      | -0.5                    | +2.9                   | V    |

| BASE, EMITTER, VCC, VDD, VTEMP, Aux0/xT0, Aux1/xT1 <sup>[2]</sup>                                                        | -0.5                    | +6                     | V    |

| SCL, MISO/SDA, MOSI, ADDR/ $\overline{CS}$ , GPIOx, CMS0, $\overline{ALRT}$ , $\overline{RESET}$ , WAKEUP <sup>[3]</sup> | DGND - 0.5              | DGND + 6               | V    |

| SDA, ALRT, GPIOx Pull-Down Current <sup>[3]</sup>                                                                        |                         | 10                     | mA   |

| ESD Rating                                                                                                               |                         | Value                  | Unit |

| Human Body Model (Tested per JS-001-2014)                                                                                |                         | 1.5                    | kV   |

| Charged Device Model (Tested per JS-002-2018)                                                                            |                         | 750                    | V    |

| Latch-Up (Tested per JESD78E; Class 2, Level A)                                                                          |                         | 100                    | mA   |

1. All voltages are specified with respect to VSS, unless otherwise noted.

2. VCP, CFET, DFET, CB[1:16], V2P5, VTEMP, and BASE pins are analog outputs and should not be driven from an external source. VCC and VDD can be driven only by the external NPN connected to the BASE and EMITTER pins.

3. ALRT, GPIO0, GPIO2, GPIO3 (configure as an output) and MISO/SDA (operating as an output) pins are digital outputs. These pins should not be driven from an external source.

### 3.2 Thermal Information

| Thermal Resistance (Typical) | θ <sub>JA</sub> (°C/W) <sup>[1]</sup> | θ <sub>JC</sub> (°C/W) <sup>[2]</sup> |

|------------------------------|---------------------------------------|---------------------------------------|

| 64 Ld QFN                    | 24                                    | 1.1                                   |

θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See TB379.

2. For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside.

| Parameter                                         | Minimum                       | Maximum | Unit |

|---------------------------------------------------|-------------------------------|---------|------|

| Maximum Continuous Power Dissipation              |                               | 400     | mW   |

| Maximum Storage Temperature Range                 | -55                           | +125    | °C   |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                               | +125    | °C   |

| Pb-Free Reflow Profile                            | Free Reflow Profile see TB493 |         |      |

### 3.3 Recommended Operation Conditions

| Parameter                                                                      | Minimum             | Maximum                 | Unit |

|--------------------------------------------------------------------------------|---------------------|-------------------------|------|

| Ambient Temperature Range (T <sub>A</sub> )                                    | -40                 | +85                     | °C   |

| Junction Temperature (T <sub>J</sub> )                                         | -40                 | +95[1]                  | °C   |

| V <sub>BAT1,</sub> V <sub>BAT2</sub> Charge Pump Enabled                       | 12                  | 55                      | V    |

| V <sub>BAT1</sub> , V <sub>BAT2</sub> Charge Pump Disabled                     | 12                  | 64                      | V    |

| DFET, CFET, VCP                                                                | V <sub>BAT2</sub>   | 66                      | V    |

| CFET, DFET                                                                     | V <sub>BAT2</sub>   | V <sub>BAT2</sub> + 11  | V    |

| VCP                                                                            | V <sub>BAT2</sub>   | V <sub>BAT2</sub> + 11  | V    |

| LDMON                                                                          | 0                   | VBAT2                   | V    |

| VC(n+1) - VC(n) (n = 0 to 15)                                                  | 2.2                 | 4.7                     | V    |

| CB(n+1) - VC(n) (n = 0 to 15)                                                  | 0                   | 6                       | V    |

| VC0                                                                            | -600                | 300                     | mV   |

| CB(n) (n = 1 to 16) <sup>[2]</sup>                                             | VC <sub>(n-1)</sub> | VC <sub>(n-1)</sub> + 5 | V    |

| CSN, DGND                                                                      | -10                 | +10                     | mV   |

| (CSP - CSN) [Current Measurement]                                              | -600                | +300                    | mV   |

| VTEMP, AUX0/xT0, AUX1/xT1                                                      | 0                   | 1.22                    | V    |

| EMITTER - V <sub>DD</sub>                                                      | 0                   | 275                     | mV   |

| SDA, ALRT, GPIOx Pull-Down Current <sup>[3]</sup>                              |                     | 2.5                     | mA   |

| GPIOx, ALRT, MOSI,MISO/SDA, SCL,ADDR/CS,<br>CMS0, WAKEUP, RESET <sup>[3]</sup> | 0                   | V <sub>DD</sub>         | V    |

1. As determined by the default IOTF Threshold.

2. VCP, CFET, DFET, CB[1:16], V2P5, VTEMP, and BASE pins are analog outputs and should not be driven from an external source. VCC and VDD can be driven only by the external NPN connected to the BASE and EMITTER pins.

3. ALRT, GPIO0, GPIO2, GPIO3 (configure as an output) and MISO/SDA (operating as an output) pins are digital outputs. These pins should not be driven from an external source.

### 3.4 Electrical Specifications

| Parameter                                              | Symbol                               | Test Conditions                                                                                              | Min <sup>[6]</sup> | Тур   | Max <sup>[6]</sup> | Unit   |

|--------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|-------|--------------------|--------|

| Power Supply (System Operation                         | on)                                  |                                                                                                              |                    | 1     |                    |        |

| V <sub>BAT</sub> Voltage Range                         | V <sub>BAT1,</sub> V <sub>BAT2</sub> | For V <sub>BAT1,</sub> V <sub>BAT2</sub>                                                                     | 12                 |       | 55                 | V      |

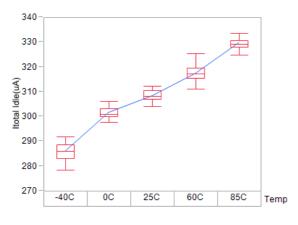

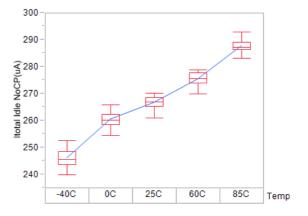

| Total Average Current<br>Consumed at VBAT1, VBAT2,     | I <sub>total</sub>                   | IDLE Mode;<br>Charge Pump On                                                                                 | 250                | 330   | 380                | μA     |

| VDD, and VCC Pins                                      |                                      | IDLE Mode;<br>Charge Pump Off                                                                                | 200                | 290   | 340                | μA     |

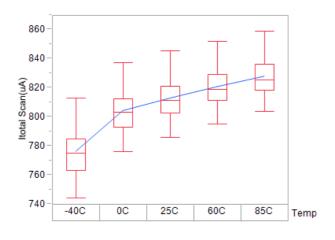

|                                                        |                                      | SCAN Mode; Charge Pump<br>and FETs on, Current<br>during VCell Scan                                          | 600                | 820   | 1000               | μA     |

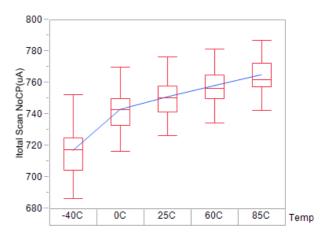

|                                                        |                                      | SCAN Mode; Charge Pump<br>and FETs off, Current<br>during VCell Scan                                         | 540                | 760   | 940                | μA     |

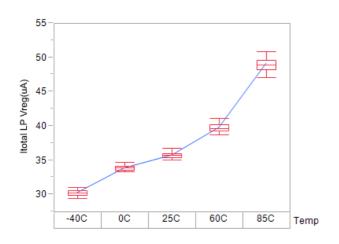

|                                                        |                                      | LOW POWER Mode;<br>Strong Reg on; LP REG = 1                                                                 |                    | 39    | 200                | μA     |

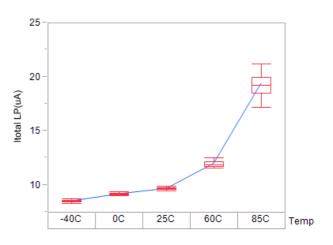

|                                                        |                                      | LOW POWER Mode; Weak<br>Reg on; LP REG = 0                                                                   |                    | 10    | 50                 | μA     |

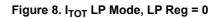

|                                                        |                                      | SHIP Mode                                                                                                    |                    | 5     | 18                 | μA     |

| Cell Measurement (0x30 - 0x4F                          | - V <sub>CELL</sub> Voltage (        | R))                                                                                                          |                    |       |                    |        |

| V <sub>CELL</sub> Measurement Error                    | V <sub>CELLME</sub>                  | $0^{\circ}$ C to + $60^{\circ}$ C; 3V to 4.5V,<br>Register 0x02 = 0x9C,<br>14 cell configuration at<br>4.5V. | -10                |       | 10                 | mV     |

| V <sub>CELL</sub> Input Leakage Current                |                                      | Not Scanning                                                                                                 | -0.3               |       | 0.3                | μA     |

| IPACK Functional Block (0x52 - 0                       | )x53 - I <sub>PACK</sub> Volta       | ge (R)) <sup>[7]</sup>                                                                                       |                    |       | I                  |        |

| I <sub>PACK</sub> Measurement Gain Error               | I <sub>PACK_GE</sub>                 | V <sub>CSP</sub> = ±200mV<br>0x03 = 0x9C                                                                     | -0.3               |       | 0.3                | %      |

| I <sub>PACK</sub> Measurement Gain Error<br>TC         | I <sub>PACK_GE_TC</sub>              | T = -40°C to +85°C<br>0x03 = 0x9C                                                                            |                    | ±30   |                    | ppm/°C |

| I <sub>PACK</sub> Measurement Offset vs<br>Common-Mode | IPACK_CMRR                           | V <sub>CMV</sub> = ±163.84mV<br>0x03 = 0x9C                                                                  |                    | ±1.6  |                    | μV/V   |

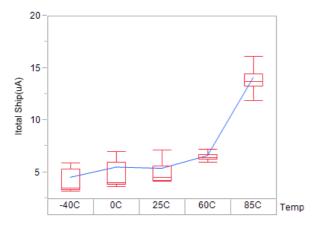

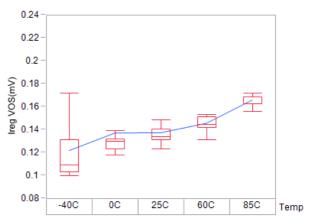

| I <sub>PACK</sub> Measurement Offset                   | I <sub>PACK_VOS</sub>                | 0x03 = 0x9C                                                                                                  | -100               | 10    | +100               | μV     |

| I <sub>PACK</sub> Measurement Offset TC                | IPACK_VOS_TC                         | T = -40°C to +85°C<br>0x03 = 0x9C                                                                            |                    | ±0.3  |                    | µV/°C  |

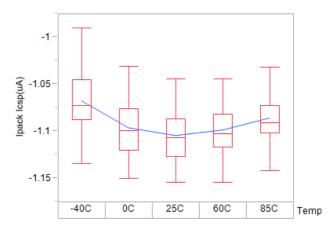

| I <sub>PACK</sub> Input Current                        | I <sub>PACK_IC</sub>                 | $V_{CSP} = V_{CSN}$                                                                                          | -15                | 1     | +15                | μA     |

|                                                        |                                      | T = -40°C to +85°C                                                                                           |                    | 0.001 |                    | µA/°C  |

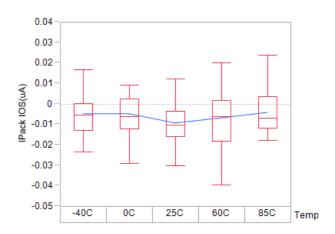

| IPACK Offset Current                                   | I <sub>os_IC</sub>                   | I <sub>CSP</sub> - I <sub>CSN</sub>                                                                          | -7.5               | 0.005 | +7.5               | μA     |

|                                                        |                                      | T = -40°C to +85°C                                                                                           |                    | 0.001 |                    | µA/°C  |

| Zero Current Threshold                                 | I <sub>Zero_THR</sub>                | Zero current threshold for charge and discharge                                                              |                    | ±200  |                    | μV     |

| Parameter                                                                                | Symbol                    | Test Conditions                                                                  | Min <sup>[6]</sup> | Тур   | Max <sup>[6]</sup> | Unit   |

|------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------|--------------------|-------|--------------------|--------|

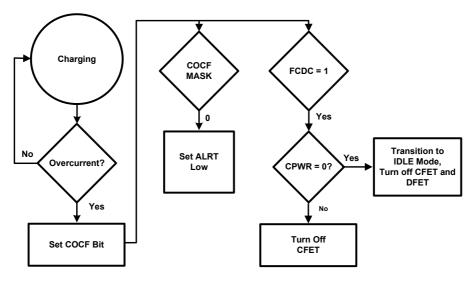

| Short-Circuit Detectors (IPACK                                                           | ault Detectors)           |                                                                                  |                    | 1     | 1                  |        |

| Discharge Short-Circuit<br>Hysteresis                                                    | SC <sub>DCHRG_Hys</sub>   |                                                                                  |                    | 20    |                    | mV     |

| Discharge Short-Circuit V <sub>OS</sub>                                                  | SC <sub>DCHRG_Vos</sub>   | Difference between setting and trigger voltage                                   |                    | 8     |                    | mV     |

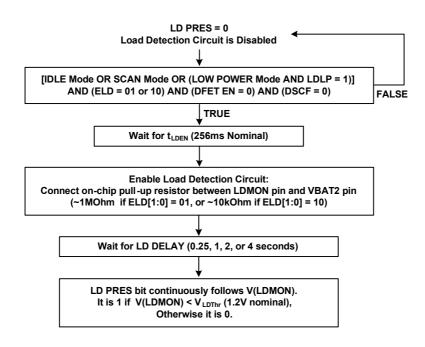

| Load Monitor Function (0x0E -                                                            | Load/Charge Ope           | rations)                                                                         |                    |       |                    |        |

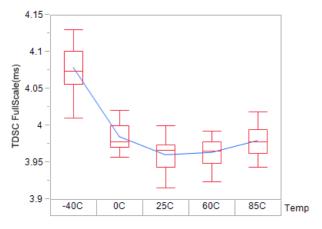

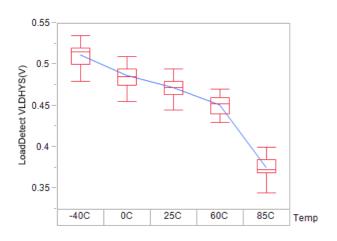

| Load Detection Threshold                                                                 | V <sub>LDThr</sub>        |                                                                                  | 0.9                | 1.2   | 1.6                | V      |

| Load Detection Hysteresis                                                                | V <sub>LDHys</sub>        |                                                                                  |                    | 100   |                    | mV     |

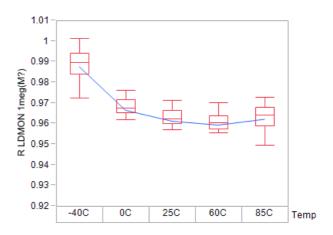

| Load Monitor Pull-Up<br>Resistance                                                       | R <sub>LDPU</sub>         | From LDMON to VBAT1<br>ELD[1:0] = 01                                             | 0.75               | 1     | 1.2                | MΩ     |

|                                                                                          |                           | From LDMON to VBAT1<br>ELD[1:0] = 10                                             | 8                  | 10    | 13.5               | kΩ     |

| Load Monitor External Isolation<br>Resistor (see Block Diagram of<br>Power FET Controls) | R <sub>LDISO</sub>        |                                                                                  | 200                |       |                    | Ω      |

| Load Monitor Enable Delay<br>Time                                                        | t <sub>LDEN</sub>         | DFET off to load detection test                                                  |                    | 256   |                    | ms     |

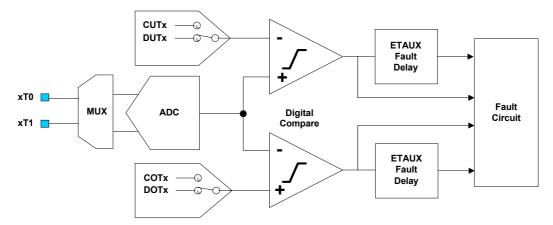

| External Temperature Measurer                                                            | nents (ETAUX De           | tectors)                                                                         |                    |       |                    |        |

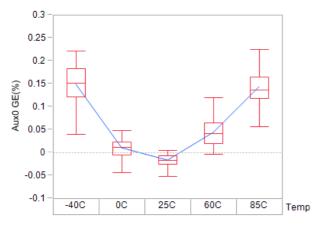

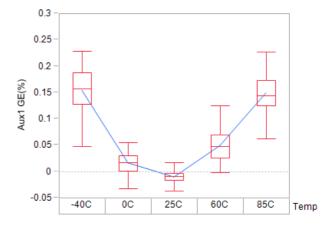

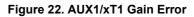

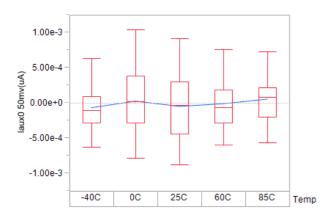

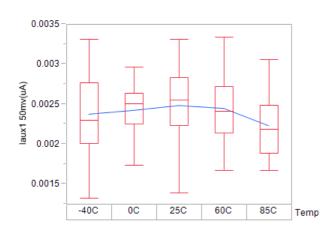

| V <sub>ETAUX</sub> Gain Error                                                            | V <sub>ETAUX_GE</sub>     | 0V to FS                                                                         | -1                 | ±0.2  | +1                 | %      |

| V <sub>ETAUX</sub> Gain Error TC                                                         | V <sub>ETAUX_GE_TC</sub>  | 0V to FS                                                                         |                    | ±35   |                    | ppm/°C |

| V <sub>ETAUX</sub> Gain Error Match                                                      | V <sub>ETAUX_GE_M</sub>   | 0V to FS                                                                         |                    | ±0.25 |                    | %      |

| V <sub>ETAUX</sub> Offset                                                                | V <sub>ETAUX_VOS</sub>    | V <sub>ETAUX</sub> = 0V                                                          |                    | -3    |                    | mV     |

| V <sub>ETAUX</sub> Offset TC                                                             | V <sub>ETAUX_VOSTC</sub>  |                                                                                  |                    | ±22   |                    | µV/°C  |

| Maximum Capacitor Connected                                                              | C <sub>ETAUX</sub>        | NTC = 10kΩ                                                                       |                    |       | 22                 | nF     |

| to xT0, xT1 (Figure 85)                                                                  |                           | NTC = 100kΩ                                                                      |                    |       | 3.9                | nF     |

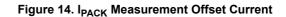

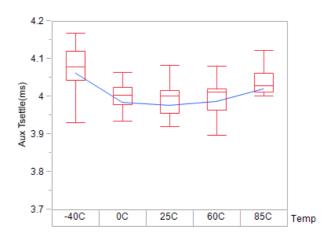

| Settling Time for VTEMP before a xT0, xT1 measurement                                    | t <sub>ETAUX_settle</sub> | V <sub>TEMP</sub> Turn on to xT0, xT1<br>measurement                             | 3.35               | 4     |                    | ms     |

| ETAUX Pull-Up Resistor                                                                   | R <sub>ETAUX</sub>        | OW Test Internal pull-up<br>resistors from xT0 and xT1<br>to VCC (AUX PULL = 1). |                    | 1.3   |                    | MΩ     |

| ETAUX Input Current                                                                      | I <sub>ETAUX</sub>        |                                                                                  | -1                 | 0.01  | +1                 | μA     |

|                                                                                          |                           | T = -40°C to 85°C                                                                |                    | 0.001 |                    | µA/°C  |

| ETAUX Open-Wire Threshold                                                                | ETAUX <sub>owThr</sub>    |                                                                                  |                    | 1.146 |                    | V      |

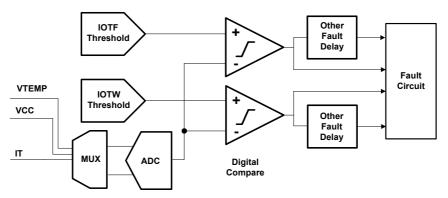

| Internal Temperature Sensor (Ir                                                          | ternal Temperatu          | ire)                                                                             |                    |       |                    |        |

| Internal Temperature Sensor<br>Measurement Range                                         | IT                        |                                                                                  | -40                |       | +85                | °C     |

| Internal Temperature Sensor<br>Output Code                                               |                           | 25°C                                                                             |                    | 0x99  |                    | Bits   |

| Internal Temperature Sensor<br>Resolution                                                | IT <sub>STEP</sub>        |                                                                                  |                    | 0.8   |                    | °C/LSB |

| Internal Temperature Error                                                               | IT <sub>ER</sub>          | 0°C to +60°C                                                                     |                    | ±5    |                    | °C     |

| Parameter                                                                   | Symbol                 | Test Conditions                                            | Min <sup>[6]</sup> | Тур   | Max <sup>[6]</sup> | Unit   |

|-----------------------------------------------------------------------------|------------------------|------------------------------------------------------------|--------------------|-------|--------------------|--------|

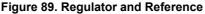

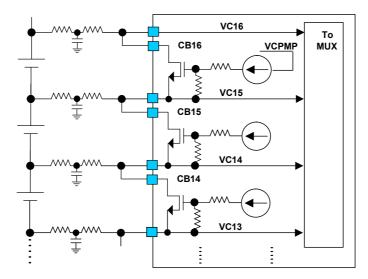

| Regulator and V <sub>TEMP</sub> (Regulato                                   | r Measurements         | and Detectors)                                             |                    |       |                    |        |

| Regulation Voltage Accuracy                                                 | REG <sub>V</sub>       | At VDD Pin, no external load                               | 3.15               | 3.3   | 3.45               | V      |

| Capacitance at the Regulator                                                | REG <sub>C</sub>       |                                                            | 1                  |       |                    | μF     |

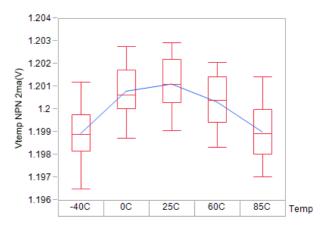

| V <sub>TEMP</sub> Voltage Accuracy                                          |                        | 0mA to 2mA load                                            | 1.189              |       | 1.221              | V      |

| V <sub>TEMP</sub> Output Impedance                                          |                        |                                                            |                    | 0.2   |                    | Ω      |

| Weak Reg Voltage at VDD                                                     |                        | SHIP or LOW POWER<br>Mode, No Load,<br>LP REG = 0          | 2.65               | 2.89  |                    | V      |

| Weak Reg Drive Current<br>Capability                                        |                        | SHIP or LOW POWER<br>Mode, LP REG = 0                      |                    | 150   |                    | μA     |

| BASE Pin Drive Current<br>capability (Ext regulator NPN<br>base drive only) | IBASE_drv              | LP REG = 1                                                 | 1                  |       |                    | mA     |

| V <sub>VCC</sub> Measurement Error                                          | V <sub>VCC_ME</sub>    |                                                            |                    | -2.0  |                    | %      |

| V <sub>VTEMP</sub> Measurement Error                                        | V <sub>VTEMP_ME</sub>  |                                                            |                    | -0.25 |                    | %      |

| I <sub>REG</sub> Measurement Gain Error                                     | IREG <sub>GE</sub>     | EMITTER = $V_{DD}$ + 50mV to<br>V <sub>DD</sub> + 200mV    |                    | 0.025 |                    | %      |

| I <sub>REG</sub> Measurement Offset                                         | IREG <sub>VOS</sub>    |                                                            |                    |       | 280                | μV     |

| Time to Switch from Strong<br>Regulator to Weak (Internal)<br>Regulator     | t <sub>REGSW</sub>     | Device transitions to SHIP<br>or LOW POWER Modes           |                    | 2.048 |                    | S      |

| Regulator and V <sub>TEMP</sub> Threshold                                   | ds (Regulator Me       | asurements and Detectors)                                  |                    | 1     | 1                  |        |

| Voltage Threshold for V <sub>TEMP</sub>                                     | VTEMP <sub>Min</sub>   |                                                            |                    | 1.1   |                    | V      |

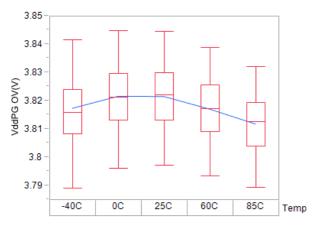

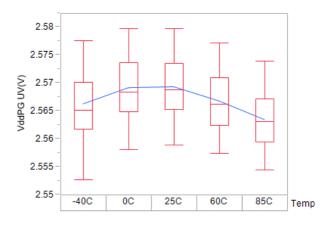

| $V_{CC}$ and $V_{DD}$ Overvoltage                                           | PG <sub>VDD_OV</sub>   |                                                            |                    | 3.83  |                    | V      |

| Threshold                                                                   | PG <sub>VCC_OV</sub>   | _                                                          |                    |       |                    |        |

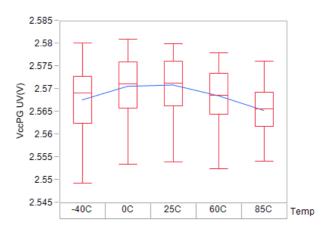

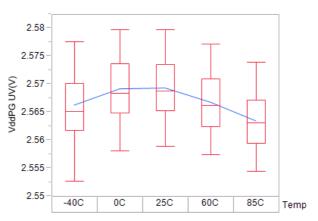

| V <sub>CC</sub> and V <sub>DD</sub> Undervoltage                            | PG <sub>VDD_UV</sub>   |                                                            |                    | 2.58  |                    | V      |

| Threshold                                                                   | PG <sub>VCC_UV</sub>   |                                                            |                    |       |                    |        |

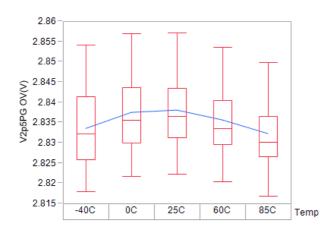

| V <sub>2P5</sub> Overvoltage Threshold                                      | PG <sub>2P5V_OV</sub>  |                                                            |                    | 2.84  |                    | V      |

| V <sub>2P5</sub> Undervoltage Threshold                                     | PG <sub>2P5V_UV</sub>  |                                                            |                    | 1.94  |                    | V      |

| V <sub>BAT1</sub> (0x20 - 0x21 - V <sub>BAT1</sub> Thre                     | sholds)                |                                                            |                    |       |                    |        |

| V <sub>BAT1</sub> Measurement Error                                         | V <sub>BAT1_ME</sub>   | 25V ≤ V <sub>BAT1</sub> ≤ 55V (0C to<br>60C)               |                    | ±0.5  |                    | %      |

| V <sub>BAT1</sub> Measurement Error TC                                      | V <sub>BAT1ME_TC</sub> |                                                            |                    | ±100  |                    | ppm/°C |

| V <sub>BAT1</sub> Input Resistance                                          | R <sub>VBAT1</sub>     |                                                            |                    | 640   |                    | kΩ     |

| Cell Balancing (Cell Balancing                                              | Registers)             | · ·                                                        |                    | •     |                    |        |

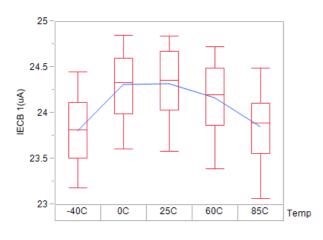

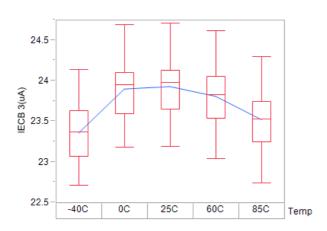

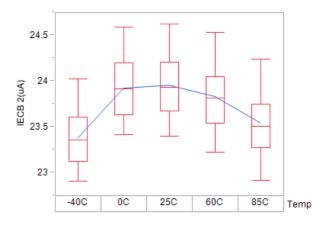

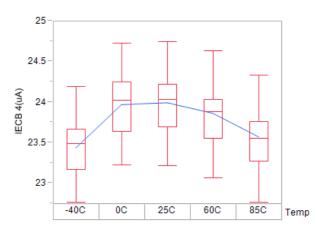

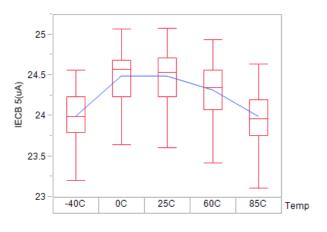

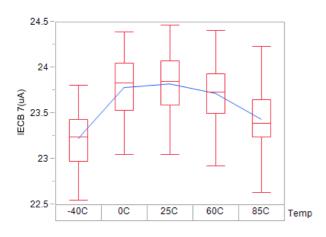

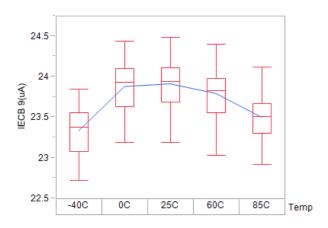

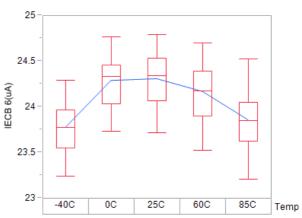

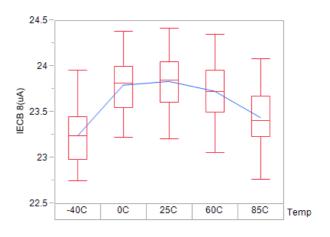

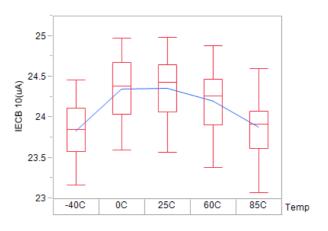

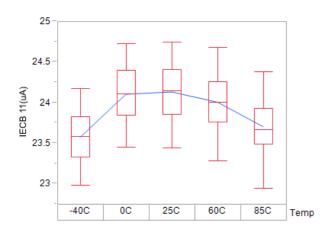

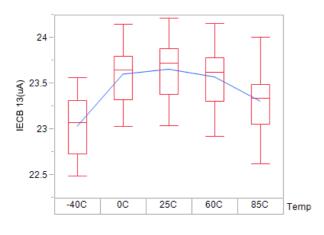

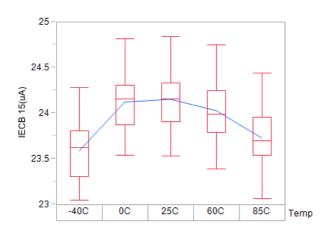

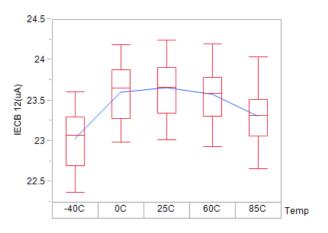

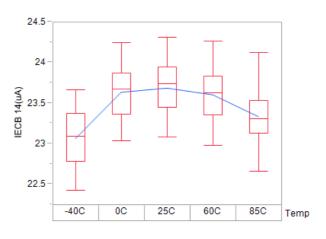

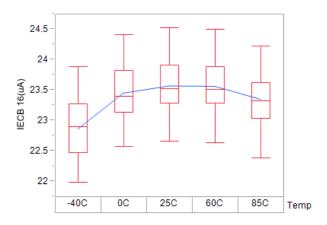

| External Cell Balance Drive<br>Current                                      | I <sub>ECB</sub>       | CB Config = 1;<br>CB <sub>n</sub> output on (n = 1 to 16)  | 21                 |       | 28                 | μA     |

| External Cell Balance Leakage<br>Current                                    | I <sub>ECB_OFF</sub>   | CB Config = 1;<br>CB <sub>n</sub> output off (n = 1 to 16) |                    | 10    |                    | nA     |

| Parameter                                                                            | Symbol                                     | Test Conditions                                                                   | Min <sup>[6]</sup> | Тур  | Max <sup>[6]</sup> | Unit  |

|--------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|--------------------|------|--------------------|-------|

| Internal Cell Balance Pin<br>Resistance CBn to VCn-1 (n = 1                          | R <sub>CB_OFF,</sub><br>R <sub>CB_ON</sub> | CB Config= 0;<br>CB <sub>n</sub> output off (n = 1 to 16)                         |                    | 4    |                    | MΩ    |

| to 16)                                                                               |                                            | CB Config= 0;                                                                     |                    | 70   |                    | Ω     |

|                                                                                      |                                            | CBn output on (n = 1 to 16)                                                       |                    |      |                    |       |

| CB Threshold Hysteresis                                                              | V <sub>CBHys</sub>                         |                                                                                   |                    | 90   |                    | mV    |

| FET Drive Control Specification                                                      | s (Power FET B                             | lock)                                                                             |                    |      |                    | •     |

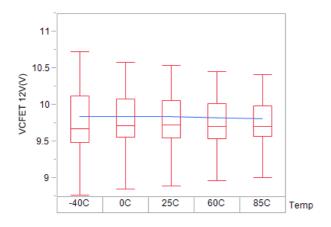

| Average Output Voltage with<br>Respect to V <sub>BAT2</sub> at DFET and<br>CFET Pins | V <sub>DFET,</sub><br>V <sub>CFET</sub>    | $12V \le V_{BAT2} \le 55V;$<br>(100µA load on Charge<br>Pump)                     | 8                  |      | 12                 | V     |

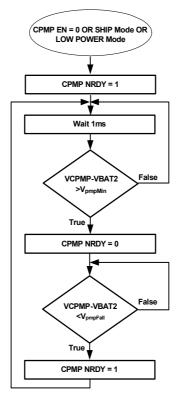

| Charge Pump Rising Voltage<br>Threshold (To clear CPMP<br>NRDY bit 0x65.5)           | V <sub>pmpMin</sub>                        | V <sub>BAT2</sub> recommended operating range                                     |                    | 11   |                    | V     |

| Charge Pump Falling Voltage<br>Threshold (To set CPMP NRDY<br>bit 0x65.5)            | V <sub>pmpFall</sub>                       | V <sub>BAT2</sub> recommended operating range                                     |                    | 5.6  |                    | V     |

| DFET Off-State Output<br>Resistance                                                  | R <sub>DFOFF</sub>                         | Resistance from DFET to LDMON, VCMP on                                            |                    | 70   |                    | Ω     |

| CFET Off-State Output<br>Resistance                                                  | R <sub>CFOFF</sub>                         | Resistance from CFET to V <sub>BAT2</sub> VCMP on                                 |                    | 70   |                    | Ω     |

| DFET On-State Output<br>Resistance                                                   | R <sub>DFON</sub>                          | Resistance from DFET to<br>VPMP, VCMP on                                          |                    | 2800 |                    | Ω     |

| CFET On-State Output<br>Resistance                                                   | R <sub>CFON</sub>                          | Resistance from CFET to VPMP, VCMP on                                             |                    | 2800 |                    | Ω     |

| Charge Pump-to-Gate<br>Capacitance Ratio (External<br>FETs)                          | C <sub>pmp</sub>                           | C <sub>pmp</sub> to (C <sub>DFET</sub> + C <sub>CFET</sub> )<br>Ratio             | 20                 |      |                    | Ratio |

| Charge Pump External Current<br>Load Capacity                                        | I <sub>pmp</sub>                           | Both $C_{FET}$ and $D_{FET}$ on                                                   | 200                |      |                    | μA    |

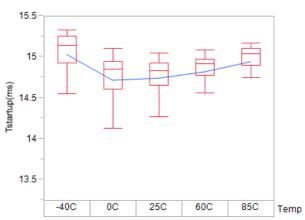

| Charge Pump Start-Up Time                                                            | t <sub>strt</sub>                          | $C_{pmp}$ = 470nF; the time it<br>takes to charge $C_{pmp}$ to<br>10V above VBAT2 |                    | 13   | 30                 | ms    |

| Open-Wire (See Open-Wire Test)                                                       | )                                          |                                                                                   |                    |      |                    |       |

| Open-Wire Resistance                                                                 | R <sub>OW</sub>                            | $VC_n$ to $VC_{n-1}$ (n = 1 to 16)                                                |                    | 8    |                    | kΩ    |

| Open-Wire Resistance<br>Connection Time                                              | t <sub>ow</sub>                            |                                                                                   |                    | 10   |                    | ms    |

| Open-Wire Detection Threshold                                                        | V <sub>OWth1</sub>                         | $VC_n$ to $VC_{n-1}$ (n = 1 to 16)                                                |                    | 0.5  |                    | V     |

| V <sub>BAT1</sub> Open-Wire Detection<br>Threshold                                   | V <sub>OWth2</sub>                         | VC16 - VBAT1                                                                      |                    | 0.3  |                    | V     |

| VSS Open-Wire Detection<br>Threshold                                                 | V <sub>OWth3</sub>                         | VC1 - VSS, VC0 - VSS                                                              |                    | 0.25 |                    | V     |

| Input Capacitance                                                                    | C <sub>OW</sub>                            | Equivalent capacitor that can be connected to the pin                             |                    |      | 200                | nF    |

| Parameter                                                      | Symbol                    | Test Conditions                                                                                | Min <sup>[6]</sup>  | Тур   | Max <sup>[6]</sup>   | Unit |

|----------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------|---------------------|-------|----------------------|------|

| System (System Operation)                                      |                           | 1                                                                                              | 1                   | 1     |                      |      |

| First Conversion ADC<br>Conversion Time                        | ADC <sub>CT1</sub>        | ADC input changes or a new trigger executes                                                    |                     | 2     |                      | ms   |

| ADC Subsequent Conversion<br>Time                              | ADC <sub>CT2</sub>        |                                                                                                |                     | 0.5   |                      | ms   |

| Communication Time Out<br>0x1B.7:6 - Communications<br>Timeout | t <sub>сом</sub>          | Maximum time allowed<br>without receiving<br>communication from the<br>Host while in IDLE mode |                     | 4.096 |                      | S    |

| LOW POWER Measurement period                                   | t <sub>LPMEAS</sub>       | Time between scans in LOW POWER Mode                                                           |                     | 2.048 |                      | S    |

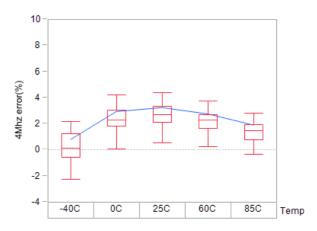

| Internal 32kHz Oscillator<br>Accuracy                          |                           |                                                                                                | -5                  | ±1    | +5                   | %    |

| Internal 4MHz Oscillator<br>Accuracy                           |                           |                                                                                                |                     | 3     |                      | %    |

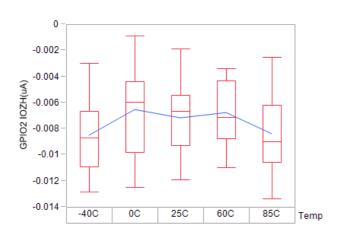

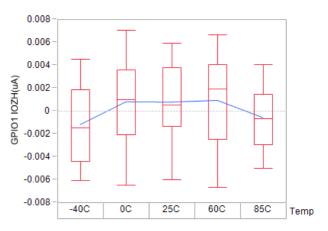

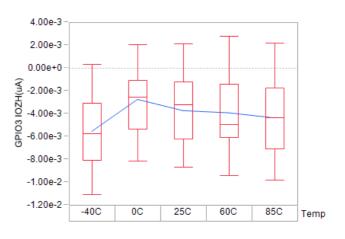

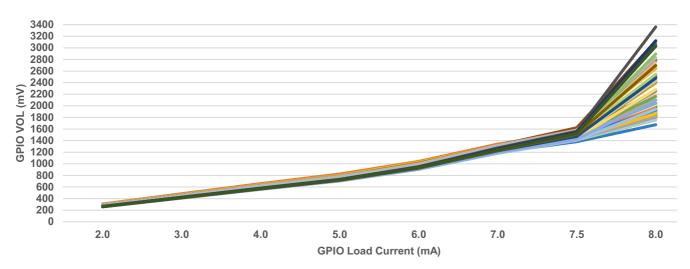

| GPIO (0x12 - ALRT and GPIO)                                    |                           | 1                                                                                              | 1                   | 1     |                      |      |

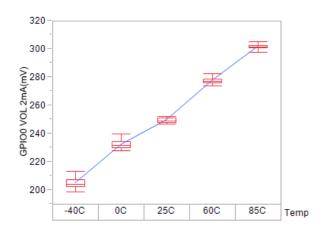

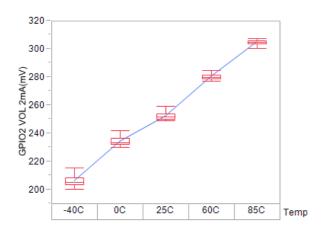

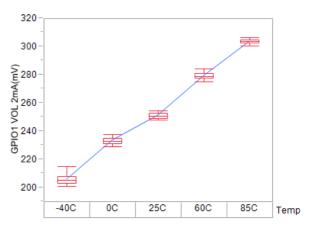

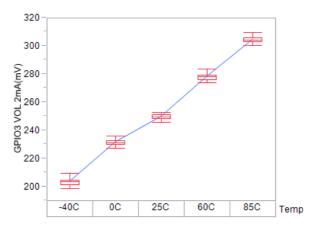

| GPIO Pins Low Level Output<br>Voltage                          | GPIO <sub>VOL</sub>       | I <sub>sink</sub> = 2mA                                                                        |                     | 0.2   | 0.4                  | V    |

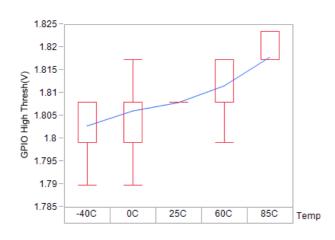

| GPIO Pin High Level Input<br>Voltage                           | GPIO <sub>VIH</sub>       |                                                                                                | 0.7xV <sub>DD</sub> |       |                      | V    |

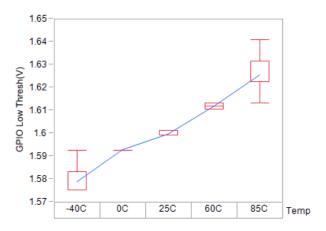

| GPIO Pin Low Level Input<br>Voltage                            | GPIO <sub>VIL</sub>       |                                                                                                |                     |       | 0.3xV <sub>DD</sub>  | V    |

| GPIO Pull-up                                                   | R <sub>GPIO_PU</sub>      |                                                                                                | 2500                |       |                      | Ω    |

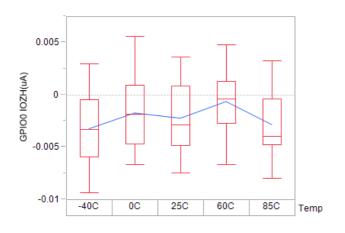

| GPIO Pins Leakage Current<br>High                              | GPIO <sub>LIH</sub>       | 3.3V applied                                                                                   | -1                  |       | +1                   | uA   |

| GPIO Pins Pulse Period                                         | GPIO <sub>pulse_per</sub> | LED Drive mode                                                                                 |                     | 10    |                      | ms   |

| GPIO Pins On-Time (Low)                                        | GPIO <sub>pulse_on</sub>  | LED Drive mode                                                                                 |                     | 2     |                      | ms   |

| CS/ADDR, CMS0                                                  |                           |                                                                                                | 1                   | •     |                      |      |

| Pins High Level Input Voltage                                  | PIN <sub>VIH</sub>        |                                                                                                | 0.7xV <sub>DD</sub> |       |                      | V    |

| Pins Low Level Input Voltage                                   | PIN <sub>VIL</sub>        |                                                                                                |                     |       | 0.3 xV <sub>DD</sub> | V    |

| Pins Leakage Current                                           | PINLIH                    | 0V to 3.3V applied                                                                             | -1                  |       | +1                   | μA   |

| ALRT (ALRT Pin (40))                                           |                           | 1                                                                                              | 1                   | 1     |                      |      |

| ALRT Pin Low Level Output<br>Voltage                           | ALRT <sub>VOL</sub>       | I <sub>sink</sub> = 2mA                                                                        |                     | 0.2   | 0.4                  | V    |

| ALRT Sink Current                                              | ALRTIOL                   | At 0.6V                                                                                        |                     | 4     |                      | mA   |

| ALRT Pin Leakage Current                                       | ALRT                      |                                                                                                | -1                  |       | +1                   | μΑ   |

| ALRT Pin Pulse Period                                          | ALRT <sub>pulse_per</sub> | ALRT Pulse EN = 1                                                                              |                     | 10    |                      | ms   |

| ALRT Pin On-Time                                               | ALRT <sub>pulse_on</sub>  | ALRT Pulse EN = 1                                                                              |                     | 2     |                      | ms   |

| WAKEUP (WAKEUP Pin (39))                                       | <u>.</u>                  | 1                                                                                              |                     |       | _ <b>.</b> I         |      |

| WAKEUP Pin High Level Input<br>Voltage                         | WKVIH                     |                                                                                                | 0.7xV <sub>DD</sub> |       |                      | V    |

| Parameter                                                        | Symbol                | Test Conditions                                                                                                                      | Min <sup>[6]</sup>    | Тур                  | Max <sup>[6]</sup>  | Unit   |

|------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|---------------------|--------|

| WAKEUP Pin Low Level Input<br>Voltage                            | WK <sub>VIL</sub>     |                                                                                                                                      |                       |                      | 0.3xV <sub>DD</sub> | V      |

| WAKEUP Pin Leakage Current                                       | WKLIH                 | 0V to 5.5V applied                                                                                                                   | -1                    |                      | +1                  | μA     |

| WAKEUP Low state pulse width                                     | $\overline{WK}_{LPw}$ | Minimum detectable pulse width                                                                                                       | 100                   |                      |                     | ns     |

| RESET (RESET Pin (38))                                           |                       |                                                                                                                                      |                       | 1                    | 1                   |        |

| RESET Pin High Level Input<br>Voltage                            | RST <sub>VIH</sub>    |                                                                                                                                      | 0.7xV <sub>DD</sub>   |                      |                     | V      |

| RESET Pin Low Level Input<br>Voltage                             | RST <sub>VIL</sub>    |                                                                                                                                      |                       |                      | 0.3xV <sub>DD</sub> | V      |

| RESET Pin Leakage Current<br>High                                | RSTLIH                | 0V to 5.5V applied                                                                                                                   | -1                    |                      | +1                  | μA     |

| Power-On Reset Voltage at<br>VBAT1<br>(Hysteresis 100mV Minimum) | V <sub>POR</sub>      |                                                                                                                                      | 4                     |                      | 7                   | V      |

| Power-On Reset Startup Time to<br>Measurement                    | t <sub>StartUp</sub>  | V <sub>BAT1</sub> > V <sub>POR</sub> , RESET<br>rising edge or soft reset to<br>first measurement<br>command                         |                       |                      | 20                  | ms     |

| Power-On Reset<br>Communication Lockout                          | t <sub>RESET</sub>    | V <sub>BAT1</sub> > V <sub>POR</sub> , RESET<br>rising edge or soft reset to<br>first serial communication<br>command activity (ACK) |                       | 200                  |                     | μs     |

| RESET Low State Pulse Width                                      | RSTLPw                |                                                                                                                                      | 100                   |                      |                     | ns     |

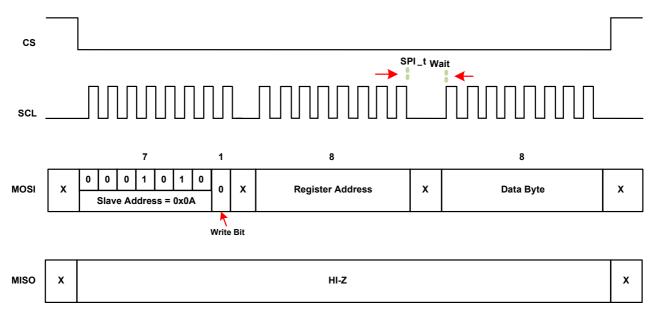

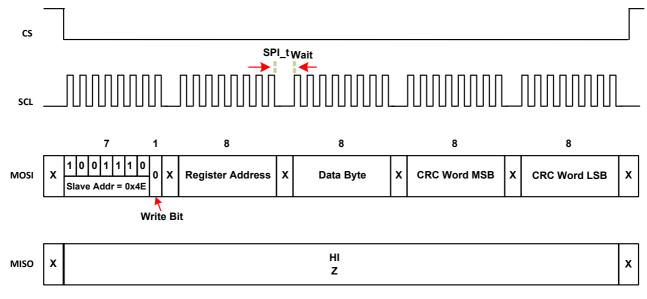

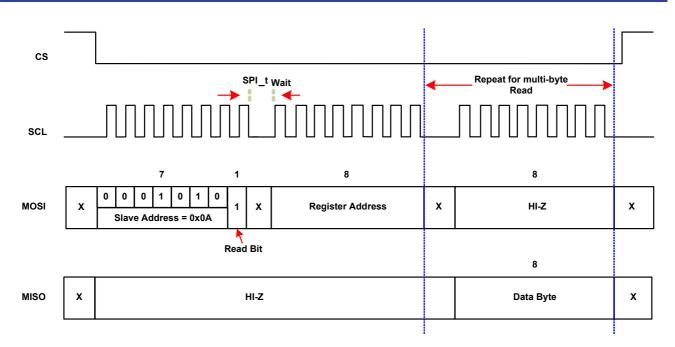

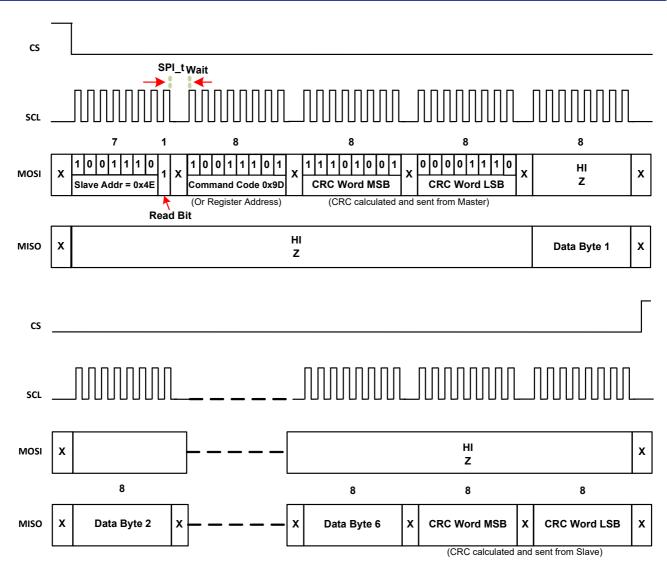

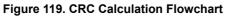

| SPI Interface Specifications (SP                                 | Serial Interface      | )<br>)                                                                                                                               |                       |                      |                     |        |

| Slave Address (7bits)<br>No CRC                                  | SA <sub>SPI</sub>     | Fixed                                                                                                                                |                       | 0001<br>010          |                     | Binary |

| Slave Address (7bits)<br>Use CRC                                 | SA <sub>SPI</sub>     | Fixed                                                                                                                                |                       | 1001<br>110          |                     | Binary |

| SCLK, MOSI, CS Input Lo<br>Voltage                               | SPI_V <sub>IL</sub>   |                                                                                                                                      |                       |                      | 0.2xV <sub>DD</sub> | V      |

| SCLK, MOSI, CS Input Hi<br>Voltage                               | SPI_V <sub>IH</sub>   |                                                                                                                                      | 0.8xV <sub>DD</sub>   |                      |                     | V      |

| SCLK, MOSI, <del>CS</del> Input<br>Hysteresis                    | SPI_V <sub>HYS</sub>  |                                                                                                                                      |                       | 0.05xV <sub>DD</sub> |                     | mV     |

| SCLK, MOSI, CS Input Current                                     | SPI_I <sub>IN</sub>   |                                                                                                                                      | -1                    |                      | +1                  | μA     |

| SCLK, MOSI, CS Input<br>Capacitance                              | SPI_C <sub>IN</sub>   |                                                                                                                                      |                       |                      | 10                  | pF     |

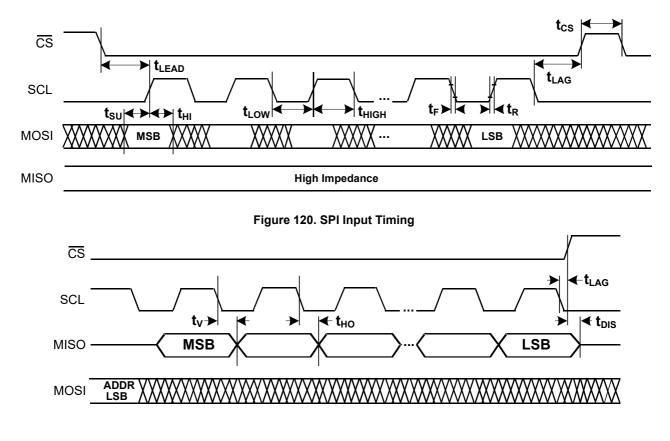

| MISO Output Lo Voltage                                           | SPI_V <sub>OL</sub>   | 2mA Sink Current                                                                                                                     | 0                     |                      | 0.4                 | V      |

| MISO Output Hi Voltage                                           | SPI_V <sub>OH</sub>   | 2mA Source Current                                                                                                                   | V <sub>DD</sub> -0.4V |                      | V <sub>DD</sub>     | V      |

| SCL Clock Frequency                                              | SPI_f <sub>SCL</sub>  |                                                                                                                                      |                       |                      | 2                   | MHz    |

| Parameter                                                   | Symbol                | Test Conditions                                                                                                                                                                                 | Min <sup>[6]</sup>  | Тур                  | Max <sup>[6]</sup>   | Unit   |

|-------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|----------------------|--------|

| Pulse Width of Input Spikes<br>Suppressed                   | SPI_t <sub>IN1</sub>  | Any pulse narrower than<br>the max spec is<br>suppressed                                                                                                                                        |                     |                      | 50                   | ns     |

| Clock High Time                                             | SPI_t <sub>HIGH</sub> |                                                                                                                                                                                                 | 200                 |                      |                      | ns     |

| Clock Low Time                                              | SPI_t <sub>LOW</sub>  |                                                                                                                                                                                                 | 200                 |                      |                      | ns     |

| Enable Lag Time                                             | SPI_t <sub>LAG</sub>  | Last data read clock edge to chip select high                                                                                                                                                   | 250                 |                      |                      | ns     |

| Time Delay Between Bytes                                    | SPI_t <sub>WAIT</sub> | Time between falling edge<br>of the clock pulse<br>corresponding to the last bit<br>of any byte, and the next<br>rising edge of the clock<br>corresponding to the first bit<br>of the next byte | 7                   |                      |                      | μs     |

| Slave Access Time                                           | SPI_T <sub>LEAD</sub> | Chip select low to SCLK rising edge                                                                                                                                                             |                     |                      | 200                  | ns     |

| Data Valid Time                                             | SPI_t <sub>V</sub>    | Clock low to MISO valid                                                                                                                                                                         |                     | 130                  | 350                  | ns     |

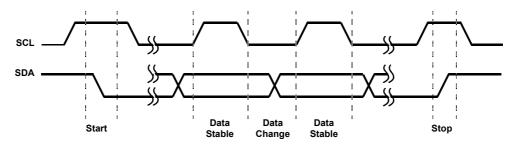

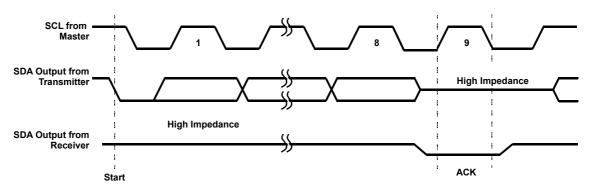

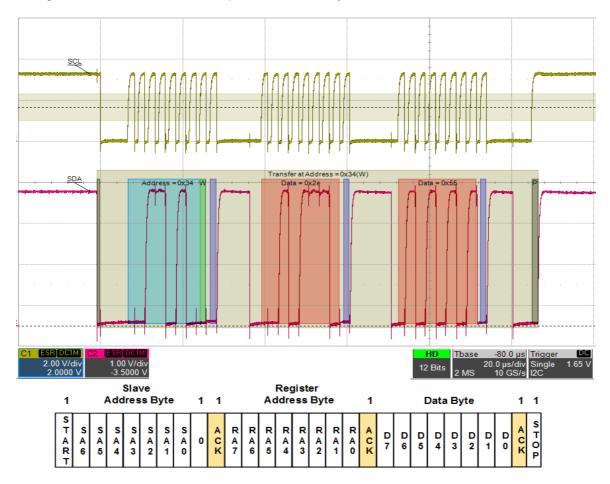

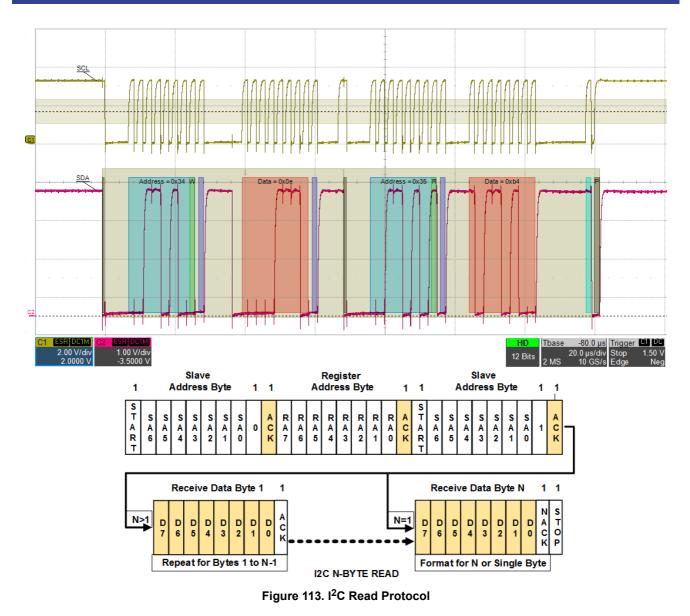

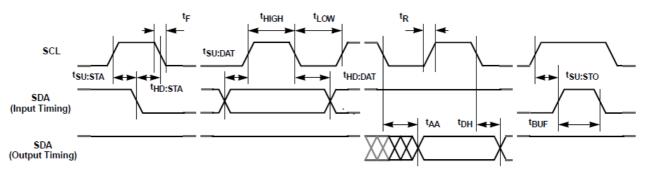

| Data Output Hold Time                                       | SPI_t <sub>HO</sub>   | Data hold time after falling edge of SCL                                                                                                                                                        | 0                   | 115                  |                      | ns     |