Материалы

Микроконтроллеры семейства RZ/N от производителя Renesas

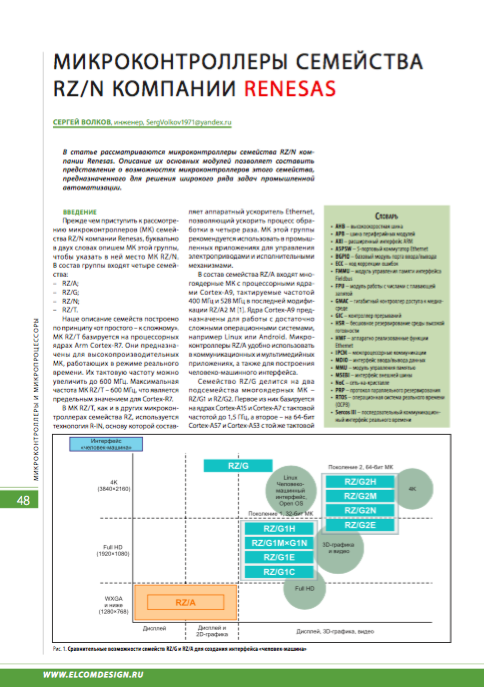

В статье рассматриваются микроконтроллеры семейства RZ/N от Renesas. Описание их основных модулей позволяет составить представление о возможностях микроконтроллеров этого семейства, предназначенного для решения широкого ряда задач промышленной автоматизации.

Многоядерные МК семейства RZ/N обычно используют для управления в промышленных системах, но они обладают и очень неплохими сетевыми возможностями. МК базируются на ядрах Cortex-а7 и Cortex-М3.

Функциональные модули микроконтроллера RZ/N1D

В микроконтроллер RZ/N1D входит двуядерный кластер Cortex-а7. Каждое ядро кластера содержит кэш команд уровня L1 емкостью 16 кбайт и точно такой же по объему кэш данных. Общий для двух ядер кэш уровня L2 имеет емкость 256 кбайт. В состав каждого из ядер входит модуль работы с плавающими числами (FPU) и модуль управления памяти (MMU), а также контроллер прерываний (GIC). Максимальная частота тактирования ядер достигает 500 МГц.

Межпроцессорные коммуникации между ядрами Cortex-a7 и Cortex-M3 осуществляются посредством трех почтовых ящиков. Модуль IPCM имеет три выхода прерываний, подключенных к каждому из трех ядер. В состав каждого почтового ящика входят семь 32-бит регистров для записи и хранения сообщений. Модуль формирует прерывания, которые могут адресоваться любому из трех процессоров или одновременно всем.

В МК встроена память SRAM с кодом коррекции ошибок ECC емкостью 2 Мбайт. У других модификаций семейства объем SRAM может достигать 6 Мбайт. Для работы с внешней памятью DDR2/3 в МК используется специальный контроллер. Благодаря многопортовой архитектуре удается эффективно распределить доступ к памяти разных типов.

Особенности контроллера DDR2/3:

- контроллер работает асинхронно с сетью NoC;

- величина адресного пространства (макс.): 2 Гбайт;

- ширина шины данных: 8 или 16 бит и 8-бит ECC;

- схема приоритетов задается программно;

- входящий адрес и тип команды для каждого порта проверяется, как указано в установочном регистре;

- можно сформировать до 16 областей адресного пространства, каждая из которых проверяется по своему правилу.

Более подробно ознакомиться с информацией Вы сможете в статье.

Автор: Сергей Волков, инженер

Источник: журнал Электронные компоненты №5 май 2020